## EE 231 Prelab 8

# **Computer Control Unit**

#### 1. Introduction

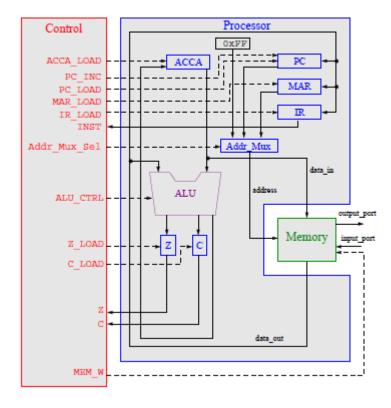

You are on the path to design your first computer. A conceptual block diagram of a simple computer is shown in Figure 1. In previous labs you have already designed the DATA MUX, the ALU, and the required registers. In this lab you will design the computer control unit. The control unit is a finite state machine. Its inputs are the instruction register, the carry, a clock pulse, and RESET. The control unit's outputs are control signals that direct the operation of the rest of the computer. The control unit can be in one of four states: RESET, FETCH, EX1 and EX2:

- RESET is the reset state. The computer gets into this state when the RESET input is low and stays in this state until the RESET input goes high.

- FETCH is the fetch cycle. The computer program is stored in memory. During the fetch cycle the next instruction is fetched from memory and loaded into the instruction register (INST).

- EX1 is the first execution cycle. Once an instruction has been loaded into INST, the control unit determines the required course of action to take based on the value of INST and the current state of the control unit.

- EX2 is the second execution cycle. Some instructions only require one execution cycle (EX1) while others require two (EX1, and EX2).

#### 1.Prelab

- 1.1. The output of the control unit depends on both the present state and the input. **What type of state machine is this?**

- 1.2.Draw the state diagram for the control unit.

**Figure 1:** Simple Computer

|   | Mnemonic                 | Operation                                         |

|---|--------------------------|---------------------------------------------------|

| 0 | LDAA addr                | Loads ACCA with the value in memory at address    |

|   | (load ACCA from mem-     | addr. C stays the same, Z changes                 |

|   | ory)                     |                                                   |

| 1 | LDAA_IMM #num            | Loads ACCA with num, the value in memory at       |

|   | (load ACCA with an im-   | the address immediately following the LDAA #num   |

|   | mediate)                 | command. C stays the same, Z changes              |

|   |                          |                                                   |

| 2 | STAA addr                | Stores the value in ACCA at memory address        |

|   | (store ACCA in memory)   | addr. C stays the same, Z changes                 |

| 3 | ADDA addr                | Adds the value in memory location addr to the     |

|   | (add ACCA and value in   | value in ACCA and saves the result in ACCA. C and |

|   | memory)                  | Z change                                          |

| 4 | SUBA addr                | Subtracts the value in memory location addr       |

|   | (subtract value in mem-  | from the value in ACCA and saves the result in    |

|   | ory from ACCA)           | ACCA. C and Z change                              |

| 5 | ANDA addr                | Perform a logical AND of the value in memory      |

|   | (logical AND of ACCA and | location addr with the value in ACCA. Save the    |

|   | value in memory)         | result in ACCA. C stays the same, Z changes       |

| 6  | ORAA addr<br>(logical OR of ACCA and<br>value in memory) | Perform a logical OR of the value in memory<br>location addr with the value in ACCA. Save the<br>result in ACCA. C stays the same, Z changes |

|----|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | CMPA addr<br>(Compares ACCA to the<br>value in addr)     | Compare ACCA to value in addr. This is done by<br>subtracting the value in addr from ACCA. ACCA<br>does not change. C and Z change           |

| 8  | (Complement ACCA)                                        | Replace the value in ACCA with its one's<br>complement. C is set to 1 and Z changes                                                          |

| 9  | INCA<br>(INCA ACCA)                                      | Increment value in ACCA. C stays the same and Z changes                                                                                      |

| A  | LSLA<br>(logical shift left ACCA)                        | Logical shift left of ACCA. C and Z change                                                                                                   |

| В  | LSRA<br>(logical shift right ACCA)                       | Logical shift right of ACCA. C and Z change                                                                                                  |

| С  | ASRA<br>(Arithmetic shift right<br>ACCA)                 | Arithmetic shift right of ACCA. C and Z change                                                                                               |

| D  | JMP addr<br>(jump)                                       | Jumps to the instruction stored in address addr.  The PC is replaced with addr. C and Z stay the                                             |

| Е  | JCS addr<br>(jump if carry set)                          | Sumps to the instruction stored in address addr<br>if C=1. If C is not set, continue with next<br>instruction. C and Z stav the same         |

| F  | JCC addr<br>(jump if carry not set)                      | Jumps to the instruction stored in address addr<br>if C=0. If C is set, continue with next instruction.<br>C and Z stay the same             |

| 10 | JEQ addr<br>(jump if Z set)                              | Jumps to the instruction stored in address addr<br>if Z=1. If Z is not set, continue with next<br>instruction. C and Z stay the same         |

**Table 1:** Computer Instructions

The outputs of the control unit are the control signals shown on the block diagram above. Except for ALU\_CTRL and MEM\_SEL, all of these signals are active low. In your Verilog code you will activate the appropriate signals at the correct times to implement the instruction the control unit is executing.

During the FETCH cycle, the control unit will fetch the next instruction from memory to determine what instruction it should execute. Thus, the FETCH cycle will be the same for all instructions where it will read the instruction from memory and latch it into the INST register. To do this, IR\_LOAD and PC\_INC should be low, and MEM\_SEL should be set to select the address from the program counter PC. With the control lines set up like this the address to the

memory will be from the PC which is the address of the next instruction to execute, and the memory output enable line will be low (active). The memory will put the data at that address on its output lines, which are the input lines to the INST register. On the next clock edge, the data from memory will be latched into the INST register, and the PC will be incremented to the next memory address. What the control unit does next will depend on the data loaded into the INST register. Here are three sample codes of how you may structure your module.

### Example 1

Consider the instruction LDAA addr where addr= $0 \times F5$ . We will further assume that the instruction is in memory address  $0 \times 80$  and  $0 \times 81$ , and that the code for LDAA addr is  $0 \times 01$ .

| PC            | Memory Address | Memory Data      |

|---------------|----------------|------------------|

| $\rightarrow$ | 80             | 01               |

|               | 81             | F5               |

|               | 82             | Next instruction |

| INST          | = ??           |                  |

| MAR           | = ??           |                  |

FETCH: During the fetch cycle the instruction register must be loaded with the instruction op code,  $0 \times 01$ . To do this the Addr MUX Sel must select the PC as the address source and the memory address  $0 \times 80$  must be read which causes its value to be placed on the DATA lines. The value on the DATA lines must be latched into IR, and the PC must be incremented. Thus during FETCH you should have PC\_INC, INST\_LOAD and Addr\_Mux\_Sel.

| PC            | Memory Address  | Memory Data      |

|---------------|-----------------|------------------|

|               | 80              | 01               |

| $\rightarrow$ | 81              | F5               |

|               | 82              | Next instruction |

| INST          | = 01 (LDAA addr | op code)         |

| MAR           | = ??            |                  |

EX1: During EX1, you must read the memory address that the PC is pointing at. By reading address 0×81 the value 0×F5 is placed on the DATA line. Then 0×F5 needs to be stored in the MAR register. Finally, the program counter should be incremented. Thus during EX1 you should have PC\_INC and MAR\_LOAD active, and Addr\_Mux\_SEL set to PC. After these steps the situation should be as shown below

| PC            | Memory Address |       | ddress | Memory Data      |

|---------------|----------------|-------|--------|------------------|

| 2010-22       |                | 80    |        | 01               |

|               |                | 81    |        | F5               |

| $\rightarrow$ |                | 02    |        | Next instruction |

| INST          | = 01           | (LDAA | addr   | op code)         |

| MAR           | = F5           |       |        |                  |

EX2: Now that MAR contains the value 0×F5, the multiplexer should select MAR as the source of the address. This address should then be read which causes the memory contents of address 0×F5 to be placed onto the DATA line. Then the ALU can load this value into ACCA. During EX2 you should have ACCA\_LOAD active, Addr\_Mux\_SEL set to MAR, and ALU\_CTL set to LOAD. When the control lines are set up like this, the value of 0×F5 will be on the address lines of the memory unit, and the data lines out of the memory will contain the data in address 0×F5. This data will be passed through the ALU to the input of ACCA.

On the next clock cycle, the value will be latched into ACCA. Note that you do not want PC INC active because PC is already pointing to the next instruction to be executed.

## Example 2

The next instruction in the program is LDAA #num where #num= $0 \times F5$ . This instruction translates as "load accumulator ACCA with the value F5". Assume the op code for LDAA # is  $0 \times 02$ . Before the program begins, the situation is as below:

| PC            | Memory Address | Memory Data      |

|---------------|----------------|------------------|

| $\rightarrow$ | 82             | 02               |

|               | 83             | F5               |

|               | 84             | Next instruction |

| INST          | = ??           |                  |

| MAR           | = ??           |                  |

FETCH: The fetch cycle is the same for this command as it was in Example 1. After the fetch cycle the situation should be:

EX1: During the EX1 cycle the PC is pointing at memory address 0×83. By reading this address, the value 0×F5 is placed on the DATA line. ACCA\_LOAD and PC\_INC, should be active, MEM SEL should be set to select PC, and the ALU\_CTRL lines should select the function which loads ACCA. When the control lines are set up like this, the value 0×83 will be on the address lines of the memory unit, and the data lines out of the memory unit will contain the data in address 0×83 (which in this example is 0×F5. This data will be passed through the ALU to the input of ACCA. On the next clock cycle the data will be latched into ACCA. There is no EX2 cycle.

The next instruction in the program is JMP addr where addr= $0 \times F5$ . Assume the op code for JMP addr is  $0 \times 12$ . Before the program begins, the situation is as below:

| PC            | Memory Address | Memory Data      |

|---------------|----------------|------------------|

| $\rightarrow$ | 84             | 12               |

|               | 85             | F5               |

|               | 86             | Next instruction |

| INST          | = ??           |                  |

| MAR           | = ??           |                  |

**FETCH**: The fetch cycle is the same for this command as it was in Example 1. After the fetch cycle the situation should be:

| PC            | Memory Address | s Memory Data    |

|---------------|----------------|------------------|

|               | 84             | 12               |

| $\rightarrow$ | 85             | F5               |

|               | 86             | Next instruction |

| INST          | = 12 (JMP addr | op code)         |

| MAR           | = ??           |                  |

EX1: During the EX1 cycle the PC is pointing at memory address 0×05. By reading this address, the value 0×F5 is placed on the DATA line. ACCA\_LOAD and PC\_LOAD, should be active, and MEM\_SEL should be set to select PC. When the control lines are set up like this, the value 0×85 will be on the address lines of the memory unit, and the data lines out of the memory unit will contain the data in address 0×85 (which in this example is 0×F5). This data will be on the input lines to PC. On the next clock cycle the data will be latched into PC. There is no EX2 cycle.