## • Interrupts and the Timer Overflow Interrupts

- Huang Sections 6.1-6.4

- Using the Timer Overflow Flag to interrupt a delay

- Introduction to Interrupts

- How to generate an interrupt when the timer overflows

- How to tell the MC9S12 where the ISR is located

- Using interrupts on the HC12

- The MC9S12 registers and stack when a TOF interrupt is received

- The MC9S12 registers and stack after a TOF interrupt is received

- Interrupt vectors for the MC9S12

- Using interrupts on the MC9S12: Assembly and C

#### What Happens When You Reset the HCS12?

- What happens to the HCS12 when you turn on power or push the reset button?

- How does the HCS12 know which instruction to execute first?

• On reset the HCS12 loads the PC with the address located at address **0xFFFE and 0xFFFF**.

• Here is what is in the memory of our MC9S12:

|             | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | B  | С  | D  | E  | F  |

|-------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| <b>FFF0</b> | F6 | EC | F6 | F0 | F6 | F4 | F6 | F8 | F6 | FC | F7 | 00 | F7 | 04 | F0 | 00 |

• On reset or power-up, the first instruction your MC9S12 will execute is the one located at address **0xF000**.

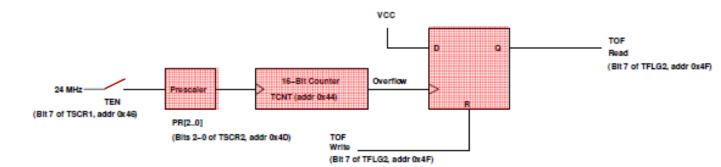

#### The MC9S12 Timer

• The MC9S12 has a 16-bit free-running counter (timer).

• The MC9S12 allows you to slow down the clock which drives the counter.

• You can **slow down the clock by dividing the 24 MHz clock** by 2, 4, 8, 16, 32, 64 or 128.

• You do this by writing to the prescaler bits (**PR2:0**) of the **Timer System Control Register 2** (**TSCR2**) Register at address **0x004D**.

2.7307 ms will be too short if you want to see lights flash. You can slow down clock by dividing it before you send it to the 16-bit counter. By setting prescaler bits P**R2**, **PR1**, **PR0** of TSCR2 you can slow down the clock:

| PR  | Divide | Freq       | <b>Overflow Rate</b> |

|-----|--------|------------|----------------------|

| 000 | 1      | 24 MHz     | 2.7307 ms            |

| 001 | 2      | 12 MHz     | 5.4613 ms            |

| 010 | 4      | 6 MHz      | 10.9227 ms           |

| 011 | 8      | 3 MHz      | 21.8453 ms           |

| 100 | 16     | 1.5 MHz    | 43.6907 ms           |

| 101 | 32     | 0.75 MHz   | 87.3813 ms           |

| 110 | 64     | 0.375 MHz  | 174.7627 ms          |

| 111 | 128    | 0.1875 MHz | 349.5253 ms          |

To set up timer so it will overflow every 87.3813 ms:

bset TSCR1,#\$80 ldaa #\$05 staa TSCR2 TSCR1 = TSCR1 | 0x80;TSCR2 = 0x05;

# EE 308 Spring 2011

TIMER OVERFLOW INTERRUPT

### Using the Timer Overflow Flag to implement a delay

• The MC9S12 timer counts at a rate set by the prescaler:

| PR2:0 | Divide | Clock Freq | Clock<br>Period | <b>Overflow Period</b> |

|-------|--------|------------|-----------------|------------------------|

| 000   | 1      | 24 MHZ     | 0.042 µs        | 2.73 ms                |

| 001   | 2      | 12 MHZ     | 0.083 µs        | 5.46 ms                |

| 010   | 4      | 6 MHZ      | 0.167 µs        | 10.92 ms               |

| 011   | 8      | 3 MHZ      | 0.333 µs        | 21.85 ms               |

| 100   | 16     | 1.5 MHZ    | 0.667 µs        | 43.69 ms               |

| 101   | 32     | 750 MHZ    | 1.333 µs        | 87.38 ms               |

| 110   | 64     | 375 MHZ    | 2.667 µs        | 174.76 ms              |

| 111   | 128    | 187.5 MHZ  | 5.333 µs        | 349.53 ms              |

• When the timer overflows it sets the TOF flag (bit 7 of the TFLG2 register).

• To clear the TOF flag write a 1 to bit 7 of the TFLG2 register, and 0 to all other bits of TFLG2:

#### TFLG2 = 0x80;

• You can implement a delay using the TOF flag by waiting for the TOF flag to be set, then clearing it:

• If the prescaler is set to **010**, you will exit the delay subroutine after 10.92 ms have passed.

Problem: Can't do anything else while waiting.

**Solution**: Have timer generate an interrupt. Program can do other things; automatically switches to service interrupt when interrupt occurs.

#### How to tell the HCS12 where the Interrupt Service Routine (ISR) is located

• You need to tell the HCS12 where to go when it receives a TOF interrupt.

• You do this by setting the TOF Interrupt Vector.

• The **TOF interrupt vector is located at 0xFFDE**. This is in flash EPROM, and is very difficult to change — you would have to modify and reload DBug-12 to change it.

• **DBug-12 redirects the interrupts to a set of vectors in RAM**, from 0x3E00 to 0x3E7F. The **TOF interrupt** is redirected to **0x3E5E**. When you get a TOF interrupt, the HCS12 initially executes code starting at **0xFFDE**. This code tells the HCS12 to load the program counter with the address in 0x3E5E. Because this address in RAM, you can change it without having to modify and reload DBug-12.

• Because the redirected interrupt vectors are in RAM, you can change them in your program.

#### How to Use Interrupts in Assembly Programs

• For our assembler, you can set the interrupt vector by including the file **hcs12.inc**. In this file, the addresses of all of the 9212 interrupt vectors are defined.

• For example, the pointer to the Timer Overflow Interrupt vector is called UserTimerOvf:

UserTimerOvf equ \$3E5E

You can set the interrupt vector to point to the interrupt service routine **toi\_isr** with the Assembly statement:

movw #toi\_isr,UserTimerOvf

• Here is a program where the interrupt vector is set in the program:

| prog: | include 'derivative.in<br>include "vectors12.in<br>equ \$2000<br>org prog<br>movw #toi_isr,UserT<br>movb #\$ff,DDRP<br>bset PTP,#\$0f<br>bset DDRJ,#\$02<br>bclr PTJ,#\$02 |                                                                     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|       | movb #\$ff,DDRB                                                                                                                                                            | ; Port B output                                                     |

|       | movb #\$80,TSCR1<br>movb #\$86,TSCR2                                                                                                                                       | ; Turn on timer<br>; Enable timer overflow interrupt, set prescaler |

|       |                                                                                                                                                                            | ; so interrupt period is 175 ms                                     |

|       | movb #\$80,TFLG2                                                                                                                                                           | ; Clear timer interrupt flag                                        |

|       | cli                                                                                                                                                                        | ; Enable interrupts                                                 |

| 11:   | wai<br>bra 11                                                                                                                                                              | ; Do nothing - go into low power mode */                            |

toi\_isr:

| inc PORTB        |                                       |

|------------------|---------------------------------------|

| movb #\$80,TFLG2 | ; Clear timer overflow interrupt flag |

| rti              |                                       |

• When the MC9S12 receives a Timer Overflow Interrupt, it finishes the current instruction, puts return address and all registers on the stack, sets the I bit of the CCR to disable interrupts, then loads the contents of UserTimerOvf (0x3E5E) into the PC.

• After executing the ISR, the rti instruction pulls the registers off the stack, and loads the PC with the return address – the program resumes from where it received the interrupt.

## **EE 308** Spring 2011

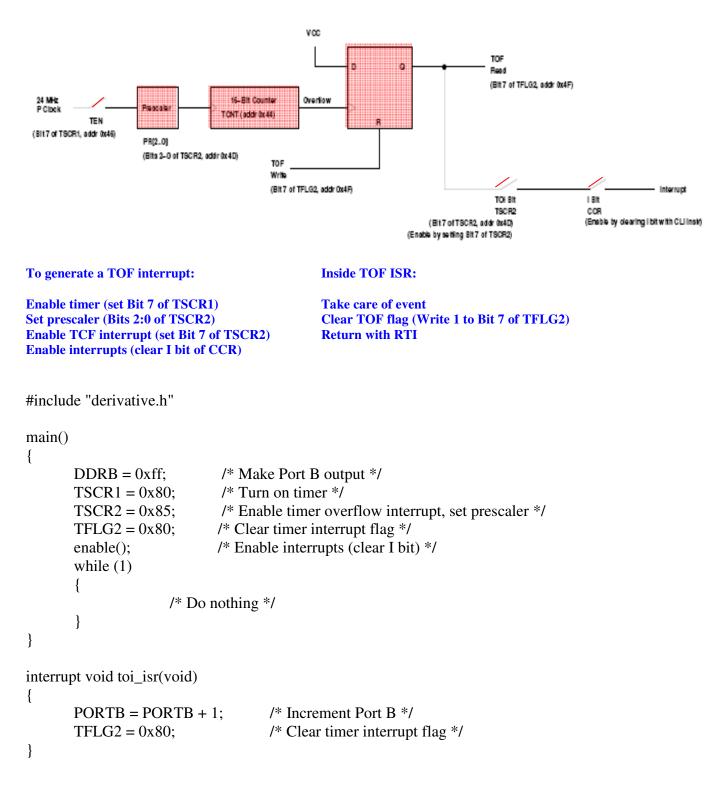

#### How to Use Interrupts in C Programs

• For our C compiler, you can set the interrupt vector by including the file **vectors12.h**. In this file, pointers to the locations of all of the MC9S12 interrupt vectors are defined.

• For example, the pointer to the Timer Overflow Interrupt vector is called **UserTimerOvf**:

#define VECTOR\_BASE 0x3E00

#define \_VEC16(off) \*(volatile unsigned short \*)(VECTOR\_BASE + off\*

#define UserTimerOvf \_VEC16(47)

The Timer Overflow vector is the 47'th vector, so it is located at

#### 0x3E00 + (47\*2) = 0x3E00 + 0x005E = 0x3E5E

You can set the interrupt vector to point to the interrupt service routine **toi\_isr**() with the C statement:

UserTimerOvf = (unsigned short) &toi\_isr;

• Here is a program where the interrupt vector is set in the program:

```

/* common defines and macros */

#include <hidef.h>

/* derivative-specific definitions */

#include "derivative.h"

/* SRAM interrupt vector redirect */

#include "vectors12.h"

#define enable() __asm(cli)

#define disable() __asm(sei)

interrupt void toi isr(void);

main()

{

DDRB = 0xff;

/* Make Port B output */

TSCR1 = 0x80;

/* Turn on timer */

/* Enable timer overflow interrupt, set prescaler */

TSCR2 = 0x86;

/*so interrupt period is 175 ms */

/* Clear timer interrupt flag */

TFLG2 = 0x80;

UserTimerOvf = (unsigned short) &toi isr;

/* Enable interrupts (clear I bit) */

enable();

while (1)

{

/* Do nothing - go into low power mode */

asm(wai);

}

}

interrupt void toi_isr(void)

{

PORTB = PORTB+1;

/* Clear timer interrupt flag */

TFLG2 = 0x80;

}

```

• The interrupt keyword tells the compiler to return from the function using the rti instruction rather than the rts instruction.

# EE 308 Spring 2011

#### **Using Interrupts on the MC9S12**

What happens when the HCS12 receives an unmasked interrupt?

- **1.** Finish current instruction

- **2.** Push all registers onto the stack

- 3. Set I bit of CCR

4. Load Program Counter from interrupt vector for particular interrupt

Most interrupts have both a specific mask and a general mask. For most interrupts the general mask is the I bit of the CCR. For the TOF interrupt the specific mask is the TOI bit of the TSCR2 register.

Before using interrupts, make sure to:

- 1. Load stack pointer

- Done for you in C by the C startup code

- **2.** Write Interrupt Service Routine

- Do whatever needs to be done to service interrupt

- Clear interrupt flag

- Exit with RTI

- Use the INTERRUPT definition in the Gnu C compiler

- **3.** Load address of interrupt service routine into interrupt vector

- 4. Do any setup needed for interrupt

- For example, for the TOF interrupt, turn on timer and set prescaler

- **5.** Enable specific interrupt.

- 6. Enable interrupts in general (clear I bit of CCR with cli instruction or enable() function

Can disable all (maskable) interrupts with the **sei** instruction or **disable**() function.

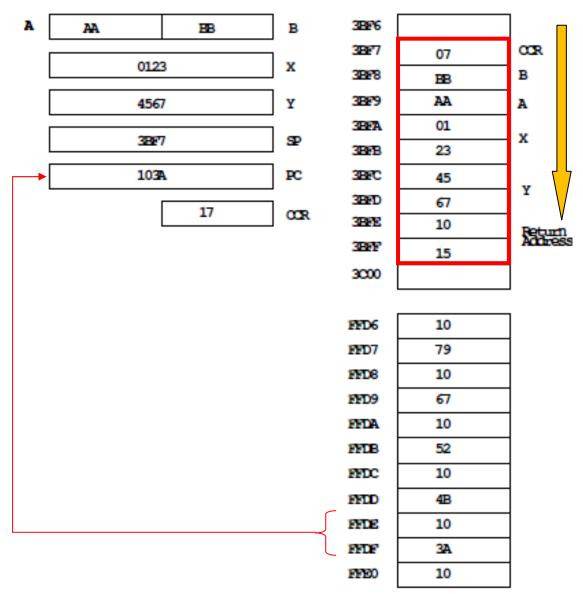

## An example of the MC9S12 registers and stack when a TOF interrupt is received

| A | AA  | BB | в   |

|---|-----|----|-----|

|   | 012 | 3  | x   |

|   | 456 | 1  | Y   |

|   | 300 | D  | sp  |

|   | 101 | 5  | PC  |

|   |     | 07 | COR |

| HC12 STATE BEFORE RECEIVING TOF INTERRUPT |

|-------------------------------------------|

|                                           |

| 3876  |  |

|-------|--|

| 3297  |  |

| 3258  |  |

| 3259  |  |

| 38974 |  |

| 3898  |  |

| 32870 |  |

| 3890  |  |

| 3898  |  |

| 3835  |  |

| 3000  |  |

|       |  |

| PFD6 | 10         |

|------|------------|

| FYD7 | 79         |

| PTD8 | 10         |

| F1D9 | ត          |

| 550% | 10         |

| 5508 | 52         |

| FFDC | 10         |

| FFDD | <b>4</b> B |

| 5503 | 10         |

| 6903 | 34         |

| 6620 | 10         |

# An example of the MC9S12 registers and stack just after a TOF interrupt is received

• All of the MC9S12 registers are pushed onto the stack, the PC is loaded with the contents of the Interrupt Vector, and the I bit of the CCR is set

#### HC12 STATE AFTER RECEIVING TOF INTERRUPT

#### **Interrupt vectors for the 68HC912B32**

The interrupt vectors for the MC9S12DP256 are located in memory from 0xFF80 to

0xFFFF.

• These vectors are programmed into Flash EEPROM and are very difficult to change

• DBug12 redirects the interrupts to a region of RAM where they are easy to change

• For example, when the MC9S12 gets a TOF interrupt:

- It loads the PC with the contents of 0xFFDE and 0xFFDF.

The program at that address tells the MC9S12 to look at address

0x3E5E and

0x3E5F.

– If there is a **0x0000** at these two addresses, <u>DBug12 gives an error</u> stating that the interrupt vector is uninitialized.

$-\mbox{ If there is anything else at these two addresses, DBug12 loads this data into the$

PC and executes the routine located there.

– To use the TOF interrupt you need to put the address of your TOF ISR at addresses 0x3E5E and 0x3E5F.

EE 308 Spring 2011

## **Commonly Used Interrupt Vectors for the MC9S12DP256**

# **EE 308** Spring 2011

| Interrupt                 | Specific                            | General | Normal     | DBug-12    |

|---------------------------|-------------------------------------|---------|------------|------------|

|                           | Mask                                | Mask    | Vector     | Vector     |

| SP12                      | SP2CR1 (SPIE, SPTIE)                | Ι       | FFBC, FFBD | SESC, SESD |

| SPI1                      | SPICR1 (SPIE, SPTIE)                | I       | FFBE, FFBF | SESE, SESF |

| IIC                       | IBCR (IBIR)                         | Ι       | FFC0, FFC1 | 3E40, 3E41 |

| BDLC                      | DLCBCR (IE)                         | Ι       | FFC2, FFC3 | 3E42, 3E43 |

| CRG Self Clock Mode       | CRGINT (SCMIE)                      | Ι       | FFC4, FFC5 | 3E44, 3E45 |

| CRG Lock                  | CRGINT (LOCKIE)                     | Ι       | FFC6, FFC7 | 3E46, 3E47 |

| Pulse Acc B Overflow      | PBCTL (PBOVI)                       | Ι       | FFC8, FFC9 | 3E48, 3E49 |

| Mod Down Ctr UnderFlow    | MCCTL (MCZI)                        | Ι       | FFCA, FFCB | 3E4A, 3E4B |

| Port H                    | PTHIF (PTHIE)                       | I       | FFCC, FFCD | SE4C, SE4D |

| Port J                    | PTJIF (PTJIE)                       | Ι       | FFCE, FFCF | SE4E, SE4F |

| ATD1                      | ATD1CTL2 (ASCIE)                    | Ι       | FFD0, FFD1 | 3E50, 3E51 |

| ATDO                      | ATDOCTL2 (ASCIE)                    | I       | FFD2, FFD3 | 3E52, 3E53 |

| SCI1                      | SC1CR2<br>(TIE, TCIE, RIE, ILIE)    | I       | FFD4, FFD5 | 3E54, 3E55 |

| SCIO                      | SCOCR2<br>(TIE, TCIE, RIE, ILIE)    | I       | FFD6, FFD7 | 3E56, 3E57 |

| SPIO                      | SPOCR1 (SPIE)                       | I       | FFD8, FFD9 | 3E58, 3E59 |

| Pulse Acc A Edge          | PACTL (PAI)                         | I       |            | SESA, SESB |

| Pulse Acc A Overflow      | PACTL (PAUVI)                       | I       | FFDC, FFDD | SESC. SESD |

| Enh Capt Timer Overflow   | TSCR2 (TOI)                         | I       | FFDE, FFDF | SESE, SESF |

| Enh Capt Timer Channel 7  | TIE (C7I)                           | Ι       | FFE0, FFE1 | 3E60, 3E61 |

| Enh Capt Timer Channel 6  | TIE (C6I)                           | I       | FFE2, FFE3 |            |

| Enh Capt Timer Channel 5  | TIE (C5I)                           | I       | FFE4, FFE5 | 3E64, 3E65 |

| Enh Capt Timer Channel 4  | TIE (C4I)                           | Ι       | FFE6, FFE7 | 3E66, 3E67 |

| Enh Capt Timer Channel 3  | TIE (C3I)                           | Ι       | FFE8, FFE9 | 3E68, 3E69 |

| Enh Capt Timer Channel 2  | TIE (C2I)                           | I       | FFEA, FFEB | SEGA, SEGB |

| Enh Capt Timer Channel 1  | TIE (C1I)                           | Ι       | FFEC, FFED | 3E6C, 3E6D |

| Enh Capt Timer Channel 0  | TIE (COI)                           | I       | FFEE, FFEF | SEGE, SEGF |

| Real Time                 | CRGINT (RTIE)                       | Ι       | FFF0, FFF1 | 3E70, 3E71 |

| IRQ                       | IRQCR (IRQEN)                       | I       | FFF2, FFF3 | 3E72, 3E73 |

| XIRQ                      | (None)                              | X       |            | 3E74, 3E75 |

| SWI                       | (None)                              | (None)  | FFF6, FFF7 | 3E76, 3E77 |

| Unimplemented Instruction | (None)                              | (None)  | FFF8, FFF9 | 3E78, 3E79 |

| COP Failure               | COPCTL<br>(CR2-CR0 COP Rate Select) | (None)  | FFFA, FFFB | SETA, SETB |

| COP Clock Moniotr Fail    | PLLCTL (CME, SCME)                  | (None)  | FFFC, FFFD | SETC, SETD |

| Reset                     | (None)                              | (None)  | FFFE, FFFF | SETE, SETF |

**Exceptions on the MC9S12**

• Exceptions are the way a processor responds to things other than the normal sequence of instructions in memory.

• Exceptions consist of such things as Reset and Interrupts.

• Interrupts allow a processor to respond to an event without constantly polling to see whether the event has occurred.

• On the HCS12 some interrupts cannot be masked — these are the Unimplemented Instruction Trap and the Software Interrupt (SWI instruction).

• XIRQ interrupt is masked with the X bit of the Condition Code Register. Once the X bit is cleared to enable the XIRQ interrupt, it cannot be set to disable it.

- The XIRQ interrupt is for external events such as power fail which must be responded to.

• The rest of the **HCS12 interrupts** are masked with the **I** bit of the **CCR**.

- All these other interrupts are also masked with a specific interrupt mask.

- This allows you to enable any of these other interrupts you want.

- The I bit can be set to 1 to disable all of these interrupts if needed.

What happens when the MC9S12 receives an unmasked interrupt?

- 1. Finish current instruction

- 2. Push all registers onto the stack

- 3. Set I bit of CCR

- 4. Load Program Counter from interrupt vector for particular interrupt

Most interrupts have both a specific mask and a general mask. For most interrupts the general mask is the I bit of the CCR. For the TOF interrupt the specific mask is the TOI bit of the **TSCR2** register.

Before using interrupts, make sure to:

- 1. Load stack pointer

- Done for you in C by the CodeWarrior startup code.

- 2. Write Interrupt Service Routine

- Do whatever needs to be done to service interrupt. Keep it short <u>do not do</u> <u>things which take a long time, such as a printf(), or wait for some external event.</u>

- Clear interrupt flag

- Exit with RTI

- Use the @interrupt function of the Cosmic C compiler

- 3. Load address of interrupt service routine into interrupt vector

- 4. Do any setup needed for interrupt

- For example, for the TOF interrupt, turn on timer and set prescaler

- 5. Enable specific interrupt

- 6. Enable interrupts in general (clear I bit of CCR with cli instruction or enable() function

Can disable all (maskable) interrupts with the sei instruction or disable() function.