- Using the MC9S12 in Expanded Mode External Ports

- S12CPUV2 Reference Manual

- Multiplexed External Bus Interface (MEBI) Module V3 Block User Guide

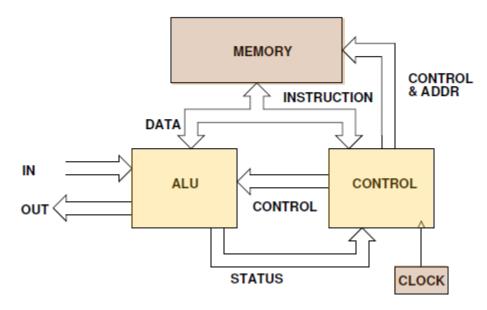

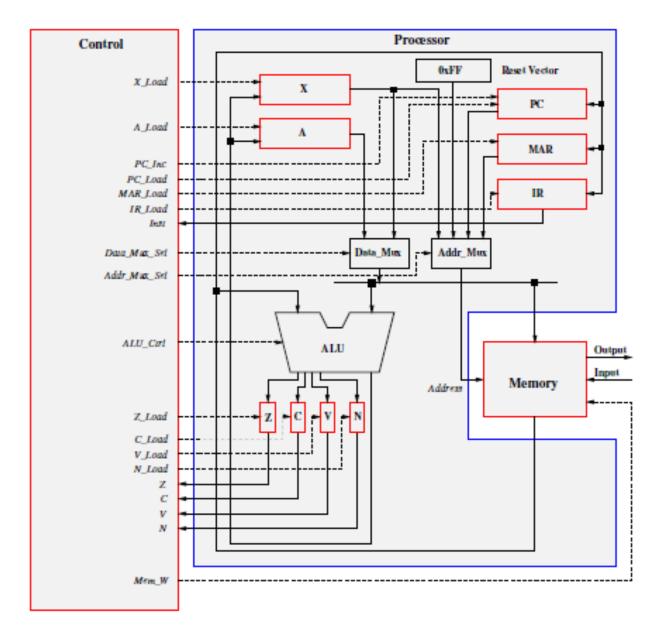

#### PRINCETON (VON NEUMAN) ARCHITECTURE

MICROPROCESSOR

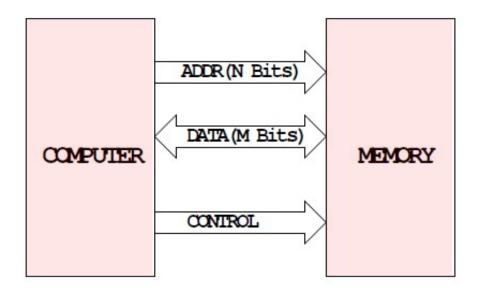

- Computer with N bit address bus can access 2 <sup>N</sup> bytes of data

- Computer with M bit data bus can access M bits of data in one memory cycle

- Value on address bus tells memory which location computer wants to read (write)

- Control lines tell memory when computer wants to read (write) data, and if access is read or write

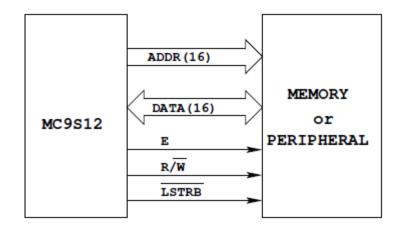

## **Address, Data and Control Buses**

• A microprocessor system uses **address**, **data** and **control** buses to communicate with external memory and memory-mapped peripherals

• The address bus determines which memory location to access

• The control bus specifies whether **the memory cycle is a read** (into microprocessor) or **a write cycle** (out of microprocessor), and specifies timing information for the cycle

• The data bus contains the data being transferred during the memory cycle

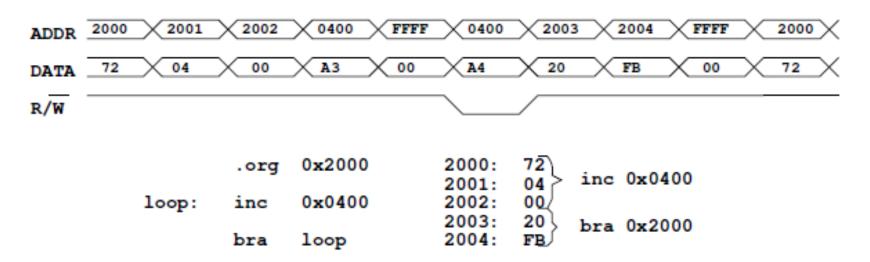

• For example, consider the following simple MC9S12 program, which continuously increments the contents of address 0x0400:

### org 0x2000 loop:inc 0x0400 bra loop

The program is stored in memory starting at memory location 0x2000

– The MC9S12 Program Counter starts at address 0x2000

– The MC9S12 reads the first instruction, inc 0x0400, located in address 0x2000 through 0x2002

The MC9S12 then reads the contents of memory location

0x0400, takes an internal memory cycle to increment the value,

then writes the new value out to address 0x0400

– The MC9S12 then reads the next instruction, *bra* 0x2000

– The MC9S12 <u>takes one memory cycle to load the program</u> <u>counter with the new value of 0x2000</u>, and to clear its internal pipeline, then reads the instruction at 0x2000 to figure out what to do next

EE 308 Spring 2013

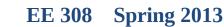

## The MC9S12 address, data and control buses

- Note: The following diagram assumes that the MC9S12 accesses one byte at a time

- The MC9S12 actually accesses two bytes (16 bits) at a time, when it can

- What actually occurs on the MC9S12 bus is a little more complicated than what is shown below

# MC9S12 ADDRESS, DATA AND CONTROL BUS (SIMPLIFIED)

MC9S12 has 16 bit address bus – can access 65536 bytes 1024 bytes = 1 kB 65536 bytes = 64 kB

MC9S12 has 16 bit data bus – can access 16 bits (2 bytes) at a time For example, the instruction LDX \$0900 will read the two bytes at address \$0900 and \$0901

Sometimes MC9S12 only accesses one byte -- e.g., LDAA \$0900 The MC9S12 accesses only the byte at address \$0900

$R/\hat{W}$  tells memory (or peripheral) if MC9S12 is reading or writing  $R/\hat{W}$  high => read  $R/\hat{W}$  low => write

E tells memory when MC9S12 is reading (writing) – synchronizes data accesses

LSTRB (together with ADDR0) tells memory if MC9S12 is accessing one or two bytes

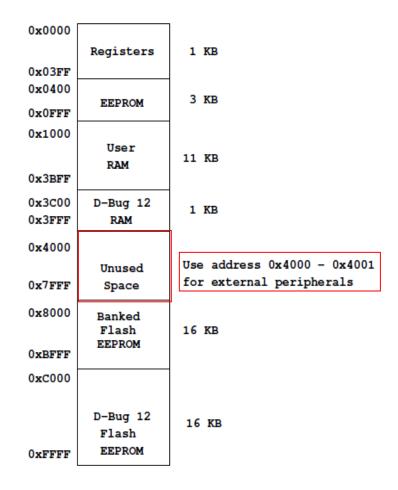

# The MC9S12 Memory Map

• The MC9S12 has address regions occupied by internal memory and peripherals

• A diagram showing which address regions are used is called a memory map

• Here is a memory map of the MC9S12DP256 <u>with no added</u> <u>memory or peripherals</u>

| 0x0000 |             | 1      |  |  |  |  |

|--------|-------------|--------|--|--|--|--|

| ux0000 | Registers   | 1 KB   |  |  |  |  |

| 0x03FF |             |        |  |  |  |  |

| 0x0400 |             | 3 KB   |  |  |  |  |

| OxOFFF | EEPROM      | JNB    |  |  |  |  |

| 0x1000 |             |        |  |  |  |  |

| Ox3BFF | User<br>RAM | 11 KB  |  |  |  |  |

|        | D. D 10     |        |  |  |  |  |

| 0x3C00 | D-Bug 12    | 1 KB   |  |  |  |  |

| 0x3FFF | RAM         |        |  |  |  |  |

| 0x4000 | Flash       | 272324 |  |  |  |  |

|        | EEPROM      | 16 KB  |  |  |  |  |

| Ox7FFF |             |        |  |  |  |  |

| 0x8000 | Banked      |        |  |  |  |  |

|        | Flash       | 16 KB  |  |  |  |  |

| OxEFFF | EEPROM      |        |  |  |  |  |

| 0xC000 |             |        |  |  |  |  |

|        |             |        |  |  |  |  |

|        | D-Bug 12    | 16 KB  |  |  |  |  |

|        | Flash       |        |  |  |  |  |

| OXFFFF | EEPROM      |        |  |  |  |  |

#### **EE 308 Spring 2013**

## The Expanded MC9S12 Memory Map

• We will add external peripherals to the MC9S12

• First, we will disable the Flash EEPROM at address 0x4000 through 0x7FFF (which we are not using anyway)

• Here is a memory map of the MC9S12DP256 with the peripherals we will add

• The peripherals will be put at 0x4000 and 0x4001

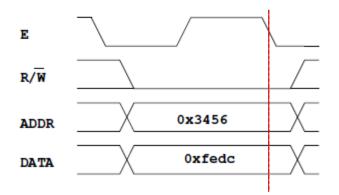

# Simplified MC9S12 Write Cycle

- When the MC9S12 writes data to memory it does the following:

- It puts the address it wants to write to on the address bus (when E-clock goes low)

- It puts the data it wants to write onto the data bus

- It brings the Read/Write  $(R/\overline{W})$  line low to indicate a write

- The MC9S12 expects the external device at the given

address will latch the data into its registers data on the falling edge of the E-clock

Example: Write 0xfedc to address 0x3456 & 3457

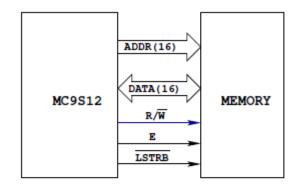

# Simplified MC9S12 Read Cycle

• <u>When the MC9S12</u> **reads** data from memory it does the following:

It puts the address it wants to read from on the address bus (when E-clock goes low)

– It brings the Read/Write  $(R/\overline{W})$  line high to indicate a read

– The MC9S12 expects the external device at the given address will put data on the data bus

– On the falling edge of the E-clock, the MC9S12 latches the data into its internal register

READ: MC9S12 puts address on address bus brings R/W high Memory puts data on data bus HC12 latches data on falling edge of E clock

Example: Read from address 0x5678 & 0x5679

#### EE 308 Spring 2013

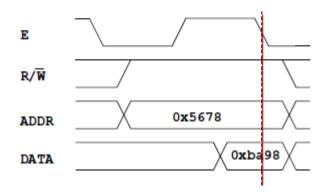

# The Real MC9S12DP256 Bus

• Up to now we have been using the MC9S12 in Single Chip Mode - In Single Chip Mode the MC9S12 does not have an external address/data bus

• The MC9S12 can be run in Expanded Mode — In Expanded Mode the MC9S12 does have an external address/data bus

• Things are a little more complicated on the real MC9S12DP256 bus than shown in the simplified diagrams above:

- The MC9S12DP256 has a multiplexed address/data bus

- The MC9S12DP256 sometimes accesses a single byte on a memory cycle, and it sometimes access two bytes on a memory cycle

|                                                                      |                                                    | ,               |                                                     |                                       |                                                         |       |                                                                                                                                                       |                                              |                                                      |                         | 9.                       |                                                                      |                                         |           |                |                                                                                                                                 |                                                               |

|----------------------------------------------------------------------|----------------------------------------------------|-----------------|-----------------------------------------------------|---------------------------------------|---------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------|-------------------------|--------------------------|----------------------------------------------------------------------|-----------------------------------------|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|                                                                      | 256K Byte Flash EEPROM                             |                 |                                                     |                                       |                                                         |       | ATD0                                                                                                                                                  |                                              | RH<br>RL<br>DA                                       | ÷                       |                          | AT                                                                   | D1                                      |           | RH<br>RL<br>DA |                                                                                                                                 | A                                                             |

|                                                                      |                                                    |                 |                                                     | vs                                    |                                                         | -     |                                                                                                                                                       | -                                            | ı                                                    | vs                      |                          | <-vss                                                                | A                                       |           |                |                                                                                                                                 |                                                               |

|                                                                      |                                                    |                 |                                                     | ANO<br>AN1<br>AN2                     | + + +                                                   |       | <pa< td=""><td>D00<br/>D01<br/>D02</td><td>A</td><td>N0<br/>N1<br/>N2</td><td>* + +</td><td></td><td>&lt;-PAD<br/>←PAD<br/>←PAD</td><td>99</td></pa<> | D00<br>D01<br>D02                            | A                                                    | N0<br>N1<br>N2          | * + +                    |                                                                      | <-PAD<br>←PAD<br>←PAD                   | 99        |                |                                                                                                                                 |                                                               |

| VDDR-+<br>VSSR-+<br>VREGEN-+<br>VDD1,2-<br>VSS1,2-                   | Voltage Regulator                                  |                 |                                                     |                                       |                                                         |       | AN3<br>AN4<br>AN5<br>AN6<br>AN7                                                                                                                       | * * * * *                                    | AD0                                                  | < PAI<br>< PAI<br>< PAI | D03<br>D04<br>D05<br>D06 | A<br>A<br>A<br>A                                                     | N3<br>N4<br>N5<br>N6                    | 4 4 4 4 4 | AD1            | <                                                                                                                               | 11<br>12<br>13<br>14                                          |

| BKGD ↔                                                               | Single-wire Background<br>Debug Module             |                 |                                                     |                                       | CPU12                                                   | PPAGE |                                                                                                                                                       |                                              |                                                      |                         |                          | PIX0<br>PIX1<br>PIX2                                                 | **<br>* *                               | ×         | ~              | PK1                                                                                                                             | XADDR14<br>XADDR15<br>XADDR16                                 |

| XFC                                                                  | PLL                                                | Re:<br>Gel      | ck and<br>set<br>neration<br>dule                   |                                       | Periodic Interrupt<br>COP Watchdog<br>Clock Monitor     |       |                                                                                                                                                       |                                              |                                                      |                         |                          | PIX3<br>PIX4<br>PIX5<br>ECS                                          | * * * *                                 | DDRK      | PTK            | ↔ PK3<br>↔ PK4                                                                                                                  | XADDR17<br>XADDR18<br>XADDR19                                 |

| ×1.2.<br>RESET ↔<br>PE0→<br>PE1→<br>PE3 ↔<br>PE3 ↔<br>PE5 ↔<br>PE6 ↔ | PTE<br>DDRE                                        | * * * * * * *   | XIRO<br>IRO<br>R/W<br>LSTRB<br>ECLK<br>MODA<br>MODB |                                       | Breakpoints<br>System<br>Integration<br>Module<br>(SIM) |       | Enha<br>Time                                                                                                                                          | ance<br>r                                    | ed C                                                 | apture                  |                          | IOC0<br>IOC1<br>IOC2<br>IOC3<br>IOC4<br>IOC5<br>IOC6<br>IOC7         | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | DORT      | РТТ            | ++ PT0<br>++ PT1<br>++ PT2<br>++ PT3<br>++ PT4<br>++ PT6<br>++ PT6<br>++ PT7                                                    |                                                               |

| PE7↔<br>TEST→                                                        | * * *                                              | **              | NOACC/5                                             | CL                                    |                                                         |       | SCI0<br>SCI1                                                                                                                                          |                                              |                                                      |                         |                          | RXD<br>TXD<br>RXD<br>TXD                                             | , + + +                                 | ŝ         | s              | ↔ PS0<br>↔ PS1<br>↔ PS2<br>↔ PS3                                                                                                |                                                               |

|                                                                      | ;;;                                                | Multiplexed Add |                                                     |                                       | Idress/Data Bus                                         |       | MISO<br>MOSI<br>SPI0 SCK<br>SS                                                                                                                        |                                              |                                                      |                         |                          |                                                                      |                                         | DDRS      | PTS            | ↔ PS4<br>↔ PS5<br>↔ PS6<br>↔ PS7                                                                                                | 0 Fin Padkage                                                 |

|                                                                      | ADDR15 PA7 +++<br>ADDR14 PA6 +++<br>ADDR13 PA5 +++ | ADDR12 PM ++    | ADDR10 PA2 ++<br>ADDR9 PA1 ++<br>ADDR8 PA0 ++       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | PTB<br>PTB<br>PTB<br>PTB<br>PTB<br>PTB<br>PTB<br>PTB    |       | BDLC<br>(J1850<br>CAN0<br>CAN1<br>CAN1                                                                                                                | ))<br>RXI<br>RXI<br>RXI<br>TXI               | CAN<br>CAN<br>CAN<br>CAN                             |                         | Made to Dark Darking     |                                                                      | * * * * * * * *                         | DDRM      | PTM            | PMO     PM1     PM2     PM3     PM4     PM6     PM6     PM7                                                                     | Signals shown in Bold are not available on tha 80 Fin Package |

| Multiplexed<br>Narrow Bus                                            | DATA7<br>DATA6<br>DATA5                            | DATA4<br>DATA3  | DATA2<br>DATA1<br>DATA0                             |                                       |                                                         | [     | IIC                                                                                                                                                   |                                              | SDA                                                  |                         | -                        | KWJO<br>KWJ1<br>KWJ6<br>KWJ7                                         | + + + +                                 | DDRJ      | PTJ            | ↔ PJ0<br>↔ PJ1<br>↔ PJ6<br>↔ PJ7                                                                                                | Signals sho                                                   |

| Internal<br>VDD1,2<br>VSS1,2<br>PLL 2.5<br>VDDPLL<br>VSSPLL          | ↓<br>↓                                             | 2.5V            | VI<br>V:<br>A/D Con<br>Voltage<br>VI                | SD)<br>SS)<br>Vei                     | ter5V &<br>gulator Reference                            |       | PWM                                                                                                                                                   | P1<br>P1<br>P1<br>P1<br>P1<br>P1<br>P1<br>P1 | NMC<br>NM2<br>NM2<br>NM3<br>NM4<br>NM6<br>NM6<br>NM6 |                         |                          | KWP0<br>KWP1<br>KWP2<br>KWP3<br>KWP4<br>KWP5<br>KWP6<br>KWP7         | ;;;;;;;;;;                              | DDRP      | РТР            | ++ PP0<br>++ PP1<br>++ PP2<br>++ PP3<br>++ PP6<br>++ PP6<br>++ PP7                                                              |                                                               |

|                                                                      | ÷                                                  |                 | VČ                                                  | e F<br>)Df<br>SSF                     |                                                         |       | SPI1<br>SPI2                                                                                                                                          | N<br>N<br>N                                  |                                                      |                         |                          | CWH0<br>CWH1<br>CWH2<br>CWH3<br>CWH3<br>CWH3<br>CWH5<br>CWH6<br>CWH7 | * * * * * * * * *                       | DDRH      | PTH            | <ul> <li>PH0</li> <li>PH1</li> <li>PH2</li> <li>PH3</li> <li>PH3</li> <li>PH4</li> <li>PH5</li> <li>PH6</li> <li>PH7</li> </ul> |                                                               |

#### Figure 1-1 MC9S12DT256 Block Diagram

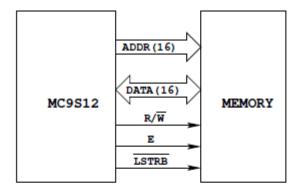

# The Multiplexed Address/Data Bus

• The MC9S12DP256 has a limited number of pins it can use

• To have full 16-bit address bus and a full 16-bit data bus the MC9S12DP256 would need to use 32 extra pins (in addition to several pins used for the control bus)

• To save pin count Motorola uses the same set of pins for several purposes

• When put into expanded mode<u>, the MC9S12 uses the pins</u> normally used for Ports A and B for its mulitplexed address and <u>data bus</u>

– When running in expanded mode you can no longer use Ports A and B as general purpose I/O lines

• The MC9S12 uses the same sixteen lines of Ports A and B for both address and data

• <u>When the E-clock is low the sixteen lines AD15-0 are used for</u> <u>address</u>

• <u>When the E-clock is high the sixteen lines AD15-0 are used for</u> <u>data</u>

# The MC9S12 Address and Data Buses

MC9S12 has 16–bit address and 16–bit data buses

It Requires 35 bits!

Not enough pins on MC9S12 to allocate 35 pins for buses and pins for all other functions

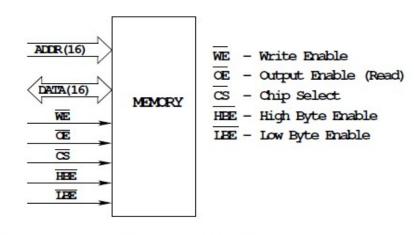

# **Memory Chip Interface**

Memory chips need separate address and data bus

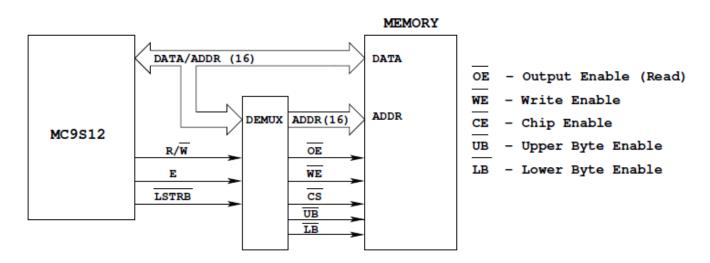

Need way to de-multiplex address and data lines from MC9S12

• Memory chips need different control lines than the MC9S12 supplies

• These control lines are:

– Chip Select – goes low when the MC9S12 is selecting memory chip

– Write Enable – goes low when the MC9S12 is writing to memory

– Output/Read Enable – goes low when the MC9S12 is reading from memory

– High Byte Enable – goes low when the MC9S12 is accessing the High Byte (Odd Address) of memory

Low Byte Enable – goes low when the MC9S12 is accessing the Low Byte (Even Address) of memory

Memory needs separate address and data busses Need way to separate address and data

# The Multiplexed Address/Data Bus

• To talk to memory chip we will need to build a de-multiplexer between the MC9S12 and the memory chip

MCS12 has 16–bit address and 16–bit data buses Requires 35 bits

Not enough pins on MC9S12 to allocate 35 pins for buses and pins for all other functions

Solution: multiplex address and data buses MC9S12 uses Ports A and B as mulitplexed address/data bus In expanded mode, you can no longer use Ports A and B for I/O

| 16-bit Bus: | <u>While E low, bus supplies address</u> (from      |

|-------------|-----------------------------------------------------|

|             | MC9S12)                                             |

|             | <u>While E high, bus supplies data (from MC9S12</u> |

|             | on write, from memory on read)                      |