# THE OXFORD SERIES IN ELECTRICAL AND COMPUTER ENGINEERING

Adel S. Sedra, Series Editor

Allen and Holberg, CMOS Analog Circuit Design, 2nd Edition

Bobrow, Elementary Linear Circuit Analysis, 2nd Edition

Bobrow, Fundamentals of Electrical Engineering, 2nd Edition

Burns and Roberts, An Introduction to Mixed-Signal IC Test and Measurement

Campbell, The Science and Engineering of Microelectronic Fabrication, 2nd Edition

Chen, Digital Signal Processing

Chen, Linear System Theory and Design, 3rd Edition

Chen, Signals and Systems, 3rd Edition

Comer, Digital Logic and State Machine Design, 3rd Edition

Comer, Microprocessor-based System Design

Cooper and McGillem, Probabilistic Methods of Signal and System Analysis, 3rd Edition

DeCarlo and Lin, Linear Circuit Analysis, 2nd Edition

Dimitrijev, Understanding Semiconductor Devices

Fortney, Principles of Electronics: Analog & Digital

Franco, Electric Circuits Fundamentals

Ghausi, Electronic Devices and Circuits: Discrete and Integrated

Guru and Hiziroglu, Electric Machinery and Transformers, 3rd Edition

Houts, Signal Analysis in Linear Systems

Jones, Introduction to Optical Fiber Communication Systems

Krein, Elements of Power Electronics

Kuo, Digital Control Systems, 3rd Edition

Lathi, Linear Systems and Signals, 2nd Edition

Lathi, Modern Digital and Analog Communications Systems, 3rd Edition

Lathi, Signal Processing and Linear Systems

Martin, Digital Integrated Circuit Design

Miner, Lines and Electromagnetic Fields for Engineers

Parhami, Computer Arithmetic

Roberts and Sedra, SPICE, 2nd Edition

Roulston, An Introduction to the Physics of Semiconductor Devices

Sadiku, Elements of Electromagnetics, 3rd Edition

Santina, Stubberud, and Hostetter, Digital Control System Design, 2nd Edition

Sarma, Introduction to Electrical Engineering

Schaumann and Van Valkenburg, Design of Analog Filters

Schwarz and Oldham, Electrical Engineering: An Introduction, 2nd Edition

Sedra and Smith, Microelectronic Circuits, 5th Edition

Stefani, Savant, Shahian, and Hostetter, Design of Feedback Control Systems, 4th Edition

Tsividis, Operation and Modeling of the MOS Transistor, 2nd Edition

Van Valkenburg, Analog Filter Design

Warner and Grung, Semiconductor Device Electronics

Wolovich, Automatic Control Systems

Yariv, Optical Electronics in Modern Communications, 5th Edition

Żak, Systems and Control

# FIFTH EDITION

# MICROELECTRONIC CIRCUITS

Adel S. Sedra

University of Waterloo

Kenneth C. Smith University of Toronto

New York Oxford

OXFORD UNIVERSITY PRESS

2004

#### Oxford University Press

Oxford New York

Auckland Bangkok Buenos Aires Cape Town Chennai

Dar es Salaam Delhi Hong Kong Istanbul Karachi Kolkata

Kuala Lumpur Madrid Melbourne Mexico City Mumbai Nairobi

São Paulo Shanghai Taipei Tokyo Toronto

Copyright © 1982, 1987, 1991, 1998, 2004 by Oxford University Press, Inc.

Published by Oxford University Press, Inc. 198 Madison Avenue, New York, New York 10016 www.oup.com

Oxford is a registered trademark of Oxford University Press

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior permission of Oxford University Press.

ISBN 0-19-514252-7

Cover Illustration: The chip shown is an inside view of a mass-produced surface-micromachined gyroscope system, integrated on a 3mm by 3mm die, and using a standard 3-m 2-V BiCMOS process suited for the harsh automotive environment. This first single-chip gyroscopic sensor, in which micro-mechanical and electronic components are intimately entwined on the same chip, provides unprecedented performance through the use of a collection of precision-directed techniques, including emphasis on differential operation (both mechanically and electronically) bolstered by trimmable thin-film resistive components. This tiny, robust, low-power, angular-rate-to-voltage transducer, having a sensitivity of 12.5mVP/s and resolution of 0.015°/s (or 50°/hour) has a myriad of applications—including automotive skid control and rollover detection, dead reckoning for GPs beaken and robot motion control, and camera-field stabilization. The complete gyroscope package, weighing 1/3 gram with a volume of 1/6 cubic centimeter, uses 30mW from a 5-V supply. Source: John A. Geen, Steven J. Sherman, John F. Chang, Stephen R. Lewis; Single-chip surface micromachined integrated Gyroscope with 50°/h Allan deviation, IEEE Journal of Solid-State Circuits, vol. 37, pp. 1860–1866, December 2002. (Originally presented at ISSCC 2002.) Photographed by John Chang, provided by John Geen, both of Analog Devices, Micromachine Products Division, Cambridge, MA, USA.

Printing number: 987654321

Printed in the United States of America on acid-free paper

# **CONDENSED TABLE OF CONTENTS**

PREFACE xxiii

# PART I DEVICES AND BASIC CIRCUITS 2

- 1 Introduction to Electronics 5

- 2 Operational Amplifiers 63

- 3 Diodes 139

- 4 MOS Field-Effect Transistors (MOSFETs) 235

- 5 Bipolar Junction Transistors (BJTs) 377

# ANALOG AND DIGITAL INTEGRATED PART II CIRCUITS 542

- 6 Single-Stage Integrated-Circuit Amplifiers 545

- 7 Differential and Multistage Amplifiers 687

- 8 Feedback 791

- 9 Operational-Amplifier and Data-Converter Circuits 871

- 10 Digital CMOS Logic Circuits 949

# PART III SELECTED TOPICS 1010

- 11 Memory and Advanced Digital Circuits 1013

- 12 Filters and Tuned Amplifiers 1083

- 13 Signal Generators and Waveform-Shaping Circuits 1165

- 14 Output Stages and Power Amplifiers 1229

# **APPENDIXES**

- A VLSI Fabrication Technology A-1

- B Two-Port Network Parameters B-1

- C Some Useful Network Theorems C-1

- D Single-Time-Constant Circuits D-1

- E s-Domain Analysis: Poles, Zeros, and Bode Plots E-1

- F Bibliography F-1

- G Standard Resistance Values and Unit Prefixes G-1

- H Answers to Selected Problems H-1

INDEX IN-1

PREFACE xxiii

# PART | DEVICES AND BASIC CIRCUITS 2

# 1 Introduction to Electronics 5

| aduct |  |

|-------|--|

- 1.1 Signals **6**

- 1.2 Frequency Spectrum of Signals 7

- 1.3 Analog and Digital Signals 10

- 1.4 Amplifiers 13

- 1.4.1 Signal Amplification 13

- 1.4.2 Amplifier Circuit Symbol 14

- 1.4.3 Voltage Gain 14

- 1.4.4 Power Gain and Current Gain 15

- 1.4.5 Expressing Gain in Decibels 15

- 1.4.6 The Amplifier Power Supplies 16

- 1.4.7 Amplifier Saturation 18

- 1.4.8 Nonlinear Transfer Characteristics and Biasing 19

- 1.4.9 Symbol Convention 22

- 1.5 Circuit Models for Amplifiers 23

- 1.5.1 Voltage Amplifiers 23

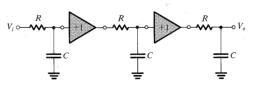

- 1.5.2 Cascaded Amplifiers 25

- 1.5.3 Other Amplifier Types 27

- 1.5.4 Relationships Between the Four Amplifier Models 27

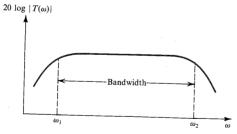

- 1.6 Frequency Response of Amplifiers 31

- 1.6.1 Measuring the Amplifier Frequency Response 31

- 1.6.2 Amplifier Bandwidth 32

- 1.6.3 Evaluating the Frequency Response of Amplifiers 33

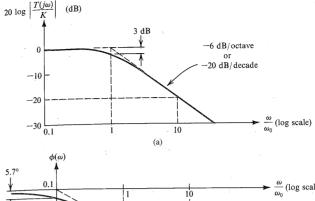

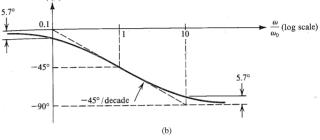

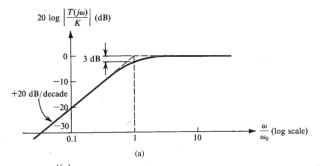

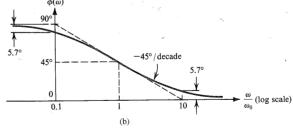

- 1.6.4 Single-Time-Constant Networks 33

- 1.6.5 Classification of Amplifiers Based on Frequency Response 38

- 1.7 Digital Logic Inverters 40

- 1.7.1 Function of the Inverter 40

- 1.7.2 The Voltage Transfer Characteristic (VTC) 41

- 1.7.3 Noise Margins 42

- 1.7.4 The Ideal VTC 43

- 1.7.5 Inverter Implementation 43

- 1.7.6 Power Dissipation 45

- 1.7.7 Propagation Delay 46

- 1.8 Circuit Simulation Using SPICE 49

- Summary 50

- Problems 51

# 2 Operational Amplifiers 63

# Introduction 63

- 2.1 The Ideal Op Amp 64

- 2.1.1 The Op-Amp Terminals 64

- 2.1.2 Function and Characteristics of the Ideal Op Amp 65

- 2.1.3 Differential and Common-Mode Signals 67

- 2.2 The Inverting Configuration 68

- 2.2.1 The Closed-Loop Gain 69

- 2.2.2 Effect of Finite Open-Loop Gain 71

- 2.2.3 Input and Output Resistances 72

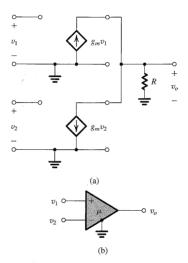

- 2.2.4 An Important Application—The Weighted Summer 75

- 2.3 The Noninverting Configuration 77

- 2.3.1 The Closed-Loop Gain 77

- 2.3.2 Characteristics of the Noninverting

- Configuration 78

- 2.3.3 Effect of Finite Open-Loop Gain 78

- 2.3.4 The Voltage Follower 79

- 2.4 Difference Amplifiers 81

- 2.4.1 A Single Op-Amp Difference Amplifier 82

- 2.4.2 A Superior Circuit—The Instrumentation Amplifier 85

- 2.5 Effect of Finite Open-Loop Gain and Bandwidth on Circuit Performance 89

- 2.5.1 Frequency Dependence of the Open-Loop Gain 89

- 2.5.2 Frequency Response of Closed-Loop Amplifiers 91

- 2.6 Large-Signal Operation of Op Amps 94

- 2.6.1 Output Voltage Saturation 94

- 2.6.1 Output Voltage Saturation 94

- 2.6.2 Output Current Limits 94

- 2.6.3 Slew Rate 95

- 2.6.4 Full-Power Bandwidth 97

- 2.7 DC Imperfections 98

- 2.7.1 Offset Voltage 98

- 2.7.2 Input Bias and Offset Currents 102

- 2.8 Integrators and Differentiators 105

- 2.8.1 The Inverting Configuration with General Impedances 105

- 2.8.2 The Inverting Integrator 107

- 2.8.3 The Op-Amp Differentiator 112

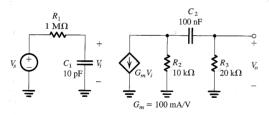

- 2.9 The SPICE Op-Amp Model and Simulation Examples 114

- 2.9.1 Linear Macromodel 115

- 2.9.2 Nonlinear Macromodel 119

- Summary 122

- Problems 123

# 3 Diodes 139

- 3.1 The Ideal Diode 140

- 3.1.1 Current-Voltage Characteristic 140

- 3.1.2 A Simple Application: The Rectifier 141

- 3.1.3 Another Application: Diode Logic Gates 144

3.2 Terminal Characteristics of Junction Diodes 147

3.3.2 Graphical Analysis Using the Exponential Model 154

3.3.3 Iterative Analysis Using the Exponential Model 154

3.2.1 The Forward-Bias Region 148 3.2.2 The Reverse-Bias Region 152

3.2.3 The Breakdown Region 152 3.3 Modeling the Diode Forward Characteristic 153

3.3.1 The Exponential Model 153

3.3.4 The Need for Rapid Analysis 155

3.3.5 The Piecewise-Linear Model 155

3.3.7 The Ideal-Diode Model 158

3.3.8 The Small-Signal Model 159

3.3.9 Use of the Diode Forward Drop in

Voltage Regulation 163

3.4 Operation in the Reverse Breakdown Region-

3.4.3 Temperature Effects 170

3.5.1 The Half-Wave Rectifier 172

3.5.2 The Full-Wave Rectifier 174

The Peak Rectifier 177

3.5.5 Precision Half-Wave Rectifier-

The Super Diode 183

3.6.3 The Voltage Doubler 189

3.7.1 Basic Semiconductor Concepts 190

3.7.5 The pn Junction Under Forward-Bias

3.8.1 The Schottky-Barrier Diode (SBD) 210

3.9 The SPICE Diode Model and Simulation Examples 212

3.8.4 Light-Emitting Diodes (LEDs) 211

3.6 Limiting and Clamping Circuits 184

3.6.1 Limiter Circuits 184

3.7 Physical Operation of Diodes 190

Conditions 204

3.7.6 Summary 208 3.8 Special Diode Types 209

3.8.2 Varactors 210

Summary 217

Problems 218

3.8.3 Photodiodes 210

3.9.1 The Diode Model 212

3.9.2 The Zener Diode Model 213

3.5.4 The Rectifier with a Filter Capacitor-

3.6.2 The Clamped Capacitor or DC Restorer 187

3.7.2 The pn Junction Under Open-Circuit Conditions 196

3.7.3 The pn Junction Under Reverse-Bias Conditions 199

3.7.4 The pn Junction in the Breakdown Region 203

3.5.3 The Bridge Rectifier 176

3.4.4 A Final Remark 171

3.3.10 Summary 165

Zener Diodes 167

3.5 Rectifier Circuits 171

3.3.6 The Constant-Voltage-Drop Model 157

3.4.1 Specifying and Modeling the Zener Diode 167

3.4.2 Use of the Zener as a Shunt Regulator 168

4 MOS Field-Effect Transistors (MOSFETs) 235

- 4.1 Device Structure and Physical Operation 236

- 4.1.1 Device Structure 236

- 4.1.2 Operation with No Gate Voltage 238

- 4.1.3 Creating a Channel for Current Flow 238

- 4.1.4 Applying a Small  $v_{\rm res}$  239

- 4.1.5 Operation as  $v_{DS}$  Is Increased 241

- 4.1.6 Derivation of the  $i_D$ - $v_{DS}$  Relationship 243

- 4.1.7 The p-Channel MOSFET 247

- 4.1.8 Complementary MOS or CMOS 247

- 4.1.9 Operating the MOS Transistor in the Subthreshold Region 248

- 4.2 Current-Voltage Characteristics 248

- 4.2.1 Circuit Symbol 248

- 4.2.2 The  $i_D$ - $v_{DS}$  Characteristics 249

- 4.2.3 Finite Output Resistance in Saturation 253

- 4.2.4 Characteristics of the p-Channel MOSFET 256

- 4.2.5 The Role of the Substrate—The Body Effect 258

- 4.2.6 Temperature Effects 259

- 4.2.7 Breakdown and Input Protection 259

- 4.2.8 Summary 260

- 4.3 MOSFET Circuits at DC 262

- 4.4 The MOSFET as an Amplifier and as a Switch 270

- 4.4.1 Large-Signal Operation—The Transfer Characteristic 271

- 4.4.2 Graphical Derivation of the Transfer Characteristic 273

- 4.4.3 Operation as a Switch 274

- 4.4.4 Operation as a Linear Amplifier 274

- 4.4.5 Analytical Expressions for the Transfer Characteristic 275

- 4.4.6 A Final Remark on Biasing 280

- 4.5 Biasing in MOS Amplifier Circuits 280

- 4.5.1 Biasing by Fixing  $V_{GS}$  280

- 4.5.2 Biasing by Fixing  $V_G$  and Connecting a Resistance

- in the Source 281

- 4.5.3 Biasing Using a Drain-to-Gate Feedback Resistor 284

- 4.5.4 Biasing Using a Constant-Current Source 285

- 4.5.5 A Final Remark 287

- 4.6 Small-Signal Operation and Models 287

- 4.6.1 The DC Bias Point 287

- 4.6.2 The Signal Current in the Drain Terminal 288

- 4.6.3 The Voltage Gain 289

- 4.6.4 Separating the DC Analysis and the Signal Analysis 290

- 4.6.5 Small-Signal Equivalent-Circuit Models 290

- 4.6.6 The Transconductance g., 292

- 4.6.7 The T Equivalent-Circuit Model 295

- 4.6.8 Modeling the Body Effect 296

- 4.6.9 Summary 297

- 4.7 Single-Stage MOS Amplifiers 299

- 4.7.1 The Basic Structure 299

- 4.7.2 Characterizing Amplifiers 301

- 4.7.3 The Common-Source (CS) Amplifier 306

- 4.7.4 The Common-Source Amplifier with a Source Resistance 309

- 4.7.5 The Common-Gate (CG) Amplifier 311

- 4.7.6 The Common-Drain or Source-Follower Amplifier 315

- 4.7.7 Summary and Comparisons 318

- 4.8 The MOSFET Internal Capacitances and High-Frequency Model 320

- 4.8.1 The Gate Capacitive Effect 321

- 4.8.2 The Junction Capacitances 322

- 4.8.3 The High-Frequency MOSFET Model 322

- 4.8.4 The MOSFET Unity-Gain Frequency  $(f_T)$  324

- 4.8.5 Summary 325

- 4.9 Frequency Response of the CS Amplifier 326

- 4.9.1 The Three Frequency Bands 326

- 4.9.2 The High-Frequency Response 328

- 4.9.3 The Low-Frequency Response 332

- 4.9.4 A Final Remark 336

- 4.10 The CMOS Digital Logic Inverter 336

- 4.10.1 Circuit Operation 337

- 4.10.2 The Voltage Transfer Characteristic 339

- 4.10.3 Dynamic Operation 342

- 4.10.4 Current Flow and Power Dissipation 345

- 4.10.5 Summary 346

- 4.11 The Depletion-Type MOSFET 346

- 4.12 The SPICE MOSFET Model and Simulation Example 351

- 4.12.1 MOSFET Models 351

- 4.12.2 MOSFET Model Parameters 352

- Summary 359

- Problems 360

# 5 Bipolar Junction Transistors (BJTs) 377

- 5.1 Device Structure and Physical Operation 378

- 5.1.1 Simplified Structure and Modes of Operation 378

- 5.1.2 Operation of the *npn* Transistor in the Active Mode 380

- 5.1.3 Structure of Actual Transistors 386

- 5.1.4 The Ebers-Moll (EM) Model 387

- 5.1.5 Operation in the Saturation Mode 390

- 5.1.6 The pnp Transistor 391

- 5.2 Current-Voltage Characteristics 392

- 5.2.1 Circuit Symbols and Conventions 392

- 5.2.2 Graphical Representation of Transistor Characteristics 397

- 5.2.3 Dependence of  $i_C$  on the Collector Voltage—The Early Effect 399

- 5.2.4 The Common-Emitter Characteristics 401

- 5.2.5 Transistor Breakdown 406

- 5.2.6 Summary 407

- 5.3 The BJT as an Amplifier and as a Switch 407

- 5.3.1 Large-Signal Operation—The Transfer Characteristic 410

- 5.3.2 Amplifier Gain 412

- 5.3.3 Graphical Analysis 415

- 5.3.4 Operation as a Switch 419

- 5.4 BJT Circuits at DC 421

- 5.5 Biasing in BJT Amplifier Circuits 436

- 5.5.1 The Classical Discrete-Circuit Bias

- Arrangement 436

- 5.5.2 A Two-Power-Supply Version of the Classical Bias Arrangement 440

- 5.5.3 Biasing Using a Collector-to-Base Feedback Resistor 441

- 5.5.4 Biasing Using a Constant-Current Source 442

- 5.6 Small-Signal Operation and Models 443

- 5.6.1 The Collector Current and the Transconductance 443

- 5.6.2 The Base Current and the Input Resistance at the Base 445

- 5.6.3 The Emitter Current and the Input Resistance at the Emitter 446

- 5.6.4 Voltage Gain 447

- 5.6.5 Separating the Signal and the DC Quantities 448

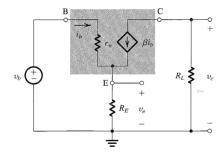

- 5.6.6 The Hybrid- $\pi$  Model 448

- 5.6.7 The T Model 449

- 5.6.8 Application of the Small-Signal Equivalent Circuits 450

- 5.6.9 Performing Small-Signal Analysis Directly on the Circuit Diagram 457

- 5.6.10 Augmenting the Small-Signal Models to Account for the Early Effect 457

- 5.6.11 Summary 458

- 5.7 Single-Stage BJT Amplifiers 460

- 5.7.1 The Basic Structure 460

- 5.7.2 Characterizing BJT Amplifiers 461

- 5.7.3 The Common-Emitter (CE) Amplifier 467

- 5.7.4 The Common-Emitter Amplifier with an Emitter Resistance 470

- 5.7.5 The Common-Base (CB) Amplifier 475

- 5.7.6 The Common-Collector (CC) Amplifier or Emitter Follower 478

- 5.7.7 Summary and Comparisons 483

- 5.8 The BJT Internal Capacitances and High-Frequency Model 485

- 5.8.1 The Base-Charging or Diffusion Capacitance C<sub>de</sub> 486

- 5.8.2 The Base–Emitter Junction Capacitance C<sub>ie</sub> 486

- 5.8.3 The Collector-Base Junction Capacitance C., 487

- 5.8.4 The High-Frequency Hybrid- $\pi$  Model 487

- 5.8.5 The Cutoff Frequency 487

- 5.8.6 Summary 490

- 5.9 Frequency Response of the Common-Emitter Amplifier 491

- 5.9.1 The Three Frequency Bands 491

- 5.9.2 The High-Frequency Response 492

- 5.9.3 The Low-Frequency Response 497

- 5.9.4 A Final Remark 503

- 5.10 The Basic BJT Digital Logic Inverter 503

- 5.10.1 The Voltage Transfer Characteristic 504

- 5.10.2 Saturated Versus Nonsaturated BJT Digital Circuits 505

- 5.11 The SPICE BJT Model and Simulation Examples 507

- 5.11.1 The SPICE Ebers-Moll Model of the BJT 507

- 5.11.2 The SPICE Gummel-Poon Model of the BJT 509

- 5.11.3 The SPICE BJT Model Parameters 510

- 5.11.4 The BJT Model Parameters BF and BR in SPICE 510

Summary 516 Problems 517

# ANALOG AND DIGITAL INTEGRATED PART II CIRCUITS 542

# 6 Single-Stage Integrated-Circuit Amplifiers 545

Introduction 545

- 6.1 IC Design Philosophy 546

- 6.2 Comparison of the MOSFET and the BJT 547

- 6.2.1 Typical Values of MOSFET Parameters 547

- 6.2.2 Typical Values of IC BJT Parameters 548

- 6.2.3 Comparison of Important Characteristics 550

- 6.2.4 Combining MOS and Bipolar Transistors—BiCMOS Circuits 561

- 6.2.5 Validity of the Square-Law MOSFET Model 562

- 6.3 IC Biasing—Current Sources, Current Mirrors, and Current-Steering Circuits 562

- 6.3.1 The Basic MOSFET Current Source 562

- 6.3.2 MOS Current-Steering Circuits 565

- 6.3.3 BJT Circuits 567

- 6.4 High-Frequency Response—General Considerations 571

- 6.4.1 The High-Frequency Gain Function 572

- 6.4.2 Determining the 3-dB Frequency  $f_H$  573

- 6.4.3 Using Open-Circuit Time Constants for the Approximate Determination of  $f_H$  575

- 6.4.4 Miller's Theorem 578

- 6.5 The Common-Source and Common-Emitter Amplifiers with Active Loads 582

- 6.5.1 The Common-Source Circuit 582

- 6.5.2 CMOS Implementation of the Common-Source Amplifier 583

- 6.5.3 The Common-Emitter Circuit 588

- 6.6 High-Frequency Response of the CS and CE Amplifiers 588

- 6.6.1 Analysis Using Miller's Theorem 589

- 6.6.2 Analysis Using Open-Circuit Time Constants 590

- 6.6.3 Exact Analysis 591

- 6.6.4 Adapting the Formulas for the Case of the CE Amplifier 595

- 6.6.5 The Situation When  $R_{\text{sig}}$  Is Low 597

- 6.7 The Common-Gate and Common-Base Amplifiers with Active Loads 600

- 6.7.1 The Common-Gate Amplifier 600

- 6.7.2 The Common-Base Amplifier 610

- 6.7.3 A Concluding Remark 613

- 6.8 The Cascode Amplifier 613

- 6.8.1 The MOS Cascode 614

- 6.8.2 Frequency Response of the MOS Cascode 618

- 6.8.3 The BJT Cascode 623

- 6.8.4 A Cascode Current Source 625

- 6.8.5 Double Cascoding 626

- 6.8.6 The Folded Cascode 627

- 6.8.7 BiCMOS Cascodes 628

- 6.9 The CS and CE Amplifiers with Source (Emitter) Degeneration 629

- 6.9.1 The CS Amplifier with a Source Resistance 629

- 6.9.2 The CE Amplifier with an Emitter Resistance 633

- 6.10 The Source and Emitter Followers 635

- 6.10.1 The Source Follower 635

- 6.10.2 Frequency Response of the Source Follower 637

- 6.10.3 The Emitter Follower 639

- 6.11 Some Useful Transistor Pairings 641

- 6.11.1 The CD-CS, CC-CE and CD-CE Configurations 641

- 6.11.2 The Darlington Configuration 645

- 6.11.3 The CC-CB and CD-CG Configurations 646

- 6.12 Current-Mirror Circuits with Improved

- Performance 649

- 6.12.1 Cascode MOS Mirrors 649

- 6.12.2 A Bipolar Mirror with Base-Current Compensation 650

- 6.12.3 The Wilson Current Mirror 651

- 6.12.4 The Wilson MOS Mirror 652

- 6.12.5 The Widlar Current Source 653

- 6.13 SPICE Simulation Examples 656

- Summary 665

- Problems 666

# 7 Differential and Multistage Amplifiers 687

- 7.1 The MOS Differential Pair 688

- 7.1.1 Operation with a Common-Mode Input

- Voltage 689

- 7.1.2 Operation with a Differential Input Voltage 691

- 7.1.3 Large-Signal Operation 693

- 7.2 Small-Signal Operation of the MOS Differential Pair 696

- 7.2.1 Differential Gain 697

- 7.2.2 Common-Mode Gain and Common-Mode Rejection Ratio (CMRR) 700

- 7.3 The BJT Differential Pair 704

- 7.3.1 Basic Operation 704

- 7.3.2 Large-Signal Operation 707

- 7.3.3 Small-Signal Operation 709

- 7.4 Other Nonideal Characteristics of the Differential Amplifier 720

- 7.4.1 Input Offset Voltage of the MOS Differential Pair 720

- 7.4.2 Input Offset Voltage of the Bipolar Differential Pair 723

- 7.4.3 Input Bias and Offset Currents of the Bipolar Pair 725

- 7.4.4 Input Common-Mode Range 726

- 7.4.5 A Concluding Remark 726

- 7.5 The Differential Amplifier with Active Load 727

- 7.5.1 Differential-to-Single-Ended Conversion 727

- 7.5.2 The Active-Loaded MOS Differential Pair 728

- 7.5.3 Differential Gain of the Active-Loaded MOS Pair 729

- 7.5.4 Common-Mode Gain and CMRR 732

- 7.5.5 The Bipolar Differential Pair with Active Load 733

- 7.6 Frequency Response of the Differential Amplifier 740 7.6.1 Analysis of the Resistively Loaded MOS Amplifier 740

- 7.6.2 Analysis of the Active-Loaded MOS Amplifier 744

- 7.7 Multistage Amplifiers 749

- 7.7.1 A Two-Stage CMOS Op Amp 749

- 7.7.2 A Bipolar Op Amp 758

- 7.8 SPICE Simulation Example 767

Summary 773 Problems 775

#### 8 Feedback 791

#### Introduction 791

- 8.1 The General Feedback Structure 792

- 8.2 Some Properties of Negative Feedback 795

- 8.2.1 Gain Desensitivity 795

- 8.2.2 Bandwidth Extension 795

- 8.2.3 Noise Reduction 796

- 8.2.4 Reduction in Nonlinear Distortion 797

- 8.3 The Four Basic Feedback Topologies 798

- 8.3.1 Voltage Amplifiers 799

- 8.3.2 Current Amplifiers 799

- 8.3.3 Transconductance Amplifiers 801

- 8.3.4 Transresistance Amplifiers 802

- 8.4 The Series-Shunt Feedback Amplifier 802

- 8.4.1 The Ideal Situation 802

- 8.4.2 The Practical Situation 804

- 8.4.3 Summary 807

- 8.5 The Series-Series Feedback Amplifier 811

- 8.5.1 The Ideal Case 811

- 8.5.2 The Practical Case 812

- 8.5.3 Summary 814

- 8.6 The Shunt-Shunt and Shunt-Series Feedback Amplifiers 818

- 8.6.1 The Shunt-Shunt Configuration 819

- 8.6.2 An Important Note 823

- 8.6.3 The Shunt-Series Configuration 823

- 8.6.4 Summary of Results 831

- 8.7 Determining the Loop Gain 831

- 8.7.1 An Alternative Approach for Finding  $A\beta$  831

- 8.7.2 Equivalence of Circuits from a Feedback-Loop Point of View 833

- 8.8 The Stability Problem 834

- 8.8.1 Transfer Function of the Feedback Amplifier 834

- 8.8.2 The Nyquist Plot 835

- 8.9 Effect of Feedback on the Amplifier Poles 836

- 8.9.1 Stability and Pole Location 837

- 8.9.2 Poles of the Feedback Amplifier 838

- 8.9.3 Amplifier with Single-Pole Response 838

- 8.9.4 Amplifier with Two-Pole Response 839

- 8.9.5 Amplifiers with Three or More Poles 843

- 8.10 Stability Study Using Bode Plots 845

- 8.10.1 Gain and Phase Margins 845

- 8.10.2 Effect of Phase Margin on Closed-Loop Response 846

- 8.10.3 An Alternative Approach for Investigating Stability 847

- 8.11 Frequency Compensation 849

- 8.11.1 Theory 850

- 8.11.2 Implementation 851

- 8.11.3 Miller Compensation and Pole Splitting 852

- 8.12 SPICE Simulation Example 855

- Summary 859

- Problems 860

# 9 Operational-Amplifier and Data-Converter Circuits 871

- 9.1 The Two-Stage CMOS Op Amp 872

- 9.1.1 The Circuit 872

- 9.1.2 Input Common-Mode Range and Output Swing 873

- 9.1.3 Voltage Gain 874

- 9.1.4 Frequency Response 876

- 9.1.5 Slew Rate 879

- 9.2 The Folded-Cascode CMOS Op Amp 883

- 9.2.1 The Circuit 883

- 9.2.2 Input Common-Mode Range and the Output Voltage Swing 885

- 9.2.3 Voltage Gain 886

- 9.2.4 Frequency Response 888

- 9.2.5 Slew Rate 888

- 9.2.6 Increasing the Input Common-Mode Range: Rail-to-Rail Input Operation 890

- 9.2.7 Increasing the Output Voltage Range: The Wide-Swing Current Mirror 892

- 9.3 The 741 Op-Amp Circuit 893

- 9.3.1 Bias Circuit 893

- 9.3.2 Short-Circuit Protection Circuitry 895

- 9.3.3 The Input Stage 895

- 9.3.4 The Second Stage 895

- 9.3.5 The Output Stage 896

- 9.3.6 Device Parameters 898

- 9.4 DC Analysis of the 741 **899**

- 9.4.1 Reference Bias Current 899

- 9.4.2 Input-Stage Bias 899

- 9.4.3 Input Bias and Offset Currents 902

- 9.4.4 Input Offset Voltage 902

- 9.4.5 Input Common-Mode Range 902

- 9.4.6 Second-Stage Bias 902

- 9.4.7 Output-Stage Bias 903

- 9.4.8 Summary 904

- 9.5 Small-Signal Analysis of the 741 905

- 9.5.1 The Input Stage 905

- 9.5.2 The Second Stage 910

- 9.5.3 The Output Stage 912

- 9.6 Gain, Frequency Response, and Slew Rate of the 741 917

- 9.6.1 Small-Signal Gain 917

- 9.6.2 Frequency Response 917

- 9.6.3 A Simplified Model 918

- 9.6.4 Slew Rate 919

- 9.6.5 Relationship Between f, and SR 920

- 9.7 Data Converters—An Introduction 922

- 9.7.1 Digital Processing of Signals 922

- 9.7.2 Sampling of Analog Signals 922

- 9.7.3 Signal Quantization 924

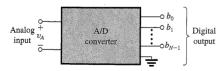

- 9.7.4 The A/D and D/A Converters as Functional Blocks 924

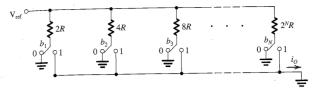

- 9.8 D/A Converter Circuits 925

- 9.8.1 Basic Circuit Using Binary-Weighted Resistors 925

- 9.8.2 R-2R Ladders 926

- 9.8.3 A Practical Circuit Implementation 927

- 9.8.4 Current Switches 928

- 9.9 A/D Converter Circuits 929

- 9.9.1 The Feedback-Type Converter 929

- 9.9.2 The Dual-Slope A/D Converter 930

- 9.9.3 The Parallel or Flash Converter 932

- 9.9.4 The Charge-Redistribution Converter 932

- 9.10 SPICE Simulation Example 934

Summary 940

Problems 941

# 10 Digital CMOS Logic Circuits 949

Introduction 949

- 10.1 Digital Circuit Design: An Overview 950

- 10.1.1 Digital IC Technologies and Logic-Circuit Families 950

- 10.1.2 Logic-Circuit Characterization 952

- 10.1.3 Styles for Digital System Design 954

- 10.1.4 Design Abstraction and Computer Aids 955

- 10.2 Design and Performance Analysis of the CMOS Inverter 955

- 10.2.1 Circuit Structure 955

- 10.2.2 Static Operation 956

- 10.2.3 Dynamic Operation 958

- 10.2.4 Dynamic Power Dissipation 961

- 10.3 CMOS Logic-Gate Circuits 963

- - 10.3.1 Basic Structure 963

- 10.3.2 The Two-Input NOR Gate 966

- 10.3.3 The Two-Input NAND Gate 966

- 10.3.4 A Complex Gate 967

- 10.3.5 Obtaining the PUN from the PDN and Vice Versa 968

- 10.3.6 The Exclusive-OR Function 969

- 10.3.7 Summary of the Synthesis Method 970

- 10.3.8 Transistor Sizing 970

- 10.3.9 Effects of Fan-In and Fan-Out on Propagation Delay 973

- 10.4 Pseudo-NMOS Logic Circuits 974

- 10.4.1 The Pseudo-NMOS Inverter 974

- 10.4.2 Static Characteristics 975

- 10.4.3 Derivation of the VTC 976

- 10.4.4 Dynamic Operation 979

- 10.4.5 Design 979

- 10.4.6 Gate Circuits 980

- 10.4.7 Concluding Remarks 980

- 10.5 Pass-Transistor Logic Circuits 982

- 10.5.1 An Essential Design Requirement 983

- 10.5.2 Operation with NMOS Transistors as Switches 984

- 10.5.3 The Use of CMOS Transmission Gates as Switches 988

- 10.5.4 Pass-Transistor Logic Circuit Examples 990

- 10.5.5 A Final Remark 991

- 10.6 Dynamic Logic Circuits 991 10.6.1 Basic Principle 992

- 10.6.2 Nonideal Effects 993

- 10.6.3 Domino CMOS Logic 996

- 10.6.4 Concluding Remarks 998

- 10.7 Spice Simulation Example 998

Summary 1002

Problems 1002

# PART III SELECTED TOPICS 1010

# 11 Memory and Advanced Digital Circuits 1013

- 11.1 Latches and Flip-flops 1014

- 11.1.1 The Latch 1014

- 11.1.2 The SR Flip-Flop 1015

- 11.1.3 CMOS Implementation of SR Flip-Flops 1016

- 11.1.4 A Simpler CMOS Implementation of the Clocked SR Flip-Flop 1019

- 11.1.5 D Flip-Flop Circuits 1019

- 11.2 Multivibrator Circuits 1021

- 11.2.1 A CMOS Monostable Circuit 1022

- 11.2.2 An Astable Circuit 1026

- 11.2.3 The Ring Oscillator 1027

- 11.3 Semiconductor Memories: Types and Architectures 1028

- 11.3.1 Memory-Chip Organization 1028

- 11.3.2 Memory-Chip Timing 1030

- 11.4 Random-Access Memory (RAM) Cells 1031

- 11.4.1 Static Memory Cell 1031

- 11.4.2 Dynamic Memory Cell 1036

- 11.5 Sense Amplifiers and Address Decoders 1038

- 11.5.1 The Sense Amplifier 1038

- 11.5.2 The Row-Address Decoder 1043

- 11.5.3 The Column-Address Decoder 1045

- 11.6 Read-Only Memory (ROM) 1046

- 11.6.1 A MOS ROM 1047

- 11.6.2 Mask-Programmable ROMs 1049

- 11.6.3 Programmable ROMs (PROMs and EPROMs) 1049

- 11.7 Emitter-Coupled Logic (ECL) 1052

- 11.7.1 The Basic Principle 1052

- 11.7.2 ECL Families 1053

- 11.7.3 The Basic Gate Circuit 1053

- 11.7.4 Voltage Transfer Characteristics 1057

- 11.7.5 Fan-Out 1061

- 11.7.6 Speed of Operation and Signal Transmission 1062

- 11.7.7 Power Dissipation 1063

- 11.7.8 Thermal Effects 1063

- 11.7.9 The Wired-OR Capability 1066

- 11.7.10 Some Final Remarks 1066

- 11.8 BiCMOS Digital Circuits 1067

- 11.8.1 The BiCMOS Inverter 1067

- 11.8.2 Dynamic Operation 1069

- 11.8.3 BiCMOS Logic Gates 1070

- 11.9 SPICE Simulation Example 1071

Summary 1076

Problems 1077

# 12 Filters and Tuned Amplifiers 1083

#### Introduction 1083

- 12.1 Filter Transmission, Types, and Specification 1084

- 12.1.1 Filter Transmission 1084

- 12.1.2 Filter Types 1085

- 12.1.3 Filter Specification 1085

- 12.2 The Filter Transfer Function 1088

- 12.3 Butterworth and Chebyshev Filters 1091

- 12.3.1 The Butterworth Filter 1091

- 12.3.2 The Chebyshev Filter 1095

- 12.4 First-Order and Second-Order Filter Functions 1098

- 12.4.1 First-Order Filters 1098

- 12.4.2 Second-Order Filter Functions 1101

- 12.5 The Second-Order LCR Resonator 1106

- 12.5.1 The Resonator Natural Modes 1106

- 12.5.2 Realization of Transmission Zeros 1107

- 12.5.3 Realization of the Low-Pass Function 1108

- 12.5.4 Realization of the High-Pass Function 1108

- 12.5.5 Realization of the Bandpass Function 1108

- 12.5.6 Realization of the Notch Functions 1110

- 12.5.7 Realization of the All-Pass Function 1111

- 12.6 Second-Order Active Filters Based on Inductor

- Replacement 1112

- 12.6.1 The Antoniou Inductance-Simulation Circuit 1112

- 12.6.2 The Op Amp-RC Resonator 1114

- 12.6.3 Realization of the Various Filter Types 1114

- 12.6.4 The All-Pass Circuit 1118

- 12.7 Second-Order Active Filters Based on the Two-Integrator-Loop Topology 1120

- 12.7.1 Derivation of the Two-Integrator-Loop Biquad 1120

- 12.7.2 Circuit Implementation 1122

- 12.7.3 An Alternative Two-Integrator-Loop Biquad Circuit 1123

- 12.7.4 Final Remarks 1125

- 12.8 Single-Amplifier Biquadratic Active Filters 1125

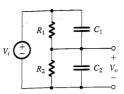

- 12.8.1 Synthesis of the Feedback Loop 1126

- 12.8.2 Injecting the Input Signal 1128

- 12.8.3 Generation of Equivalent Feedback Loops 1130

- 12.9 Sensitivity 1133

- 12.10 Switched-Capacitor Filters 1136

- 12.10.1 The Basic Principle 1136

- 12.10.2 Practical Circuits 1137

- 12.10.3 A Final Remark 1141

- 12.11 Tuned Amplifiers 1141

- 12.11.1 The Basic Principle 1141

- 12.11.2 Inductor Losses 1143

- 12.11.3 Use of Transformers 1144

- 12.11.4 Amplifiers with Multiple Tuned Circuits 1145

- 12.11.5 The Cascode and the CC-CB Cascade 1146

- 12.11.6 Synchronous Tuning 1147

- 12.11.7 Stagger-Tuning 1148

- 12.12 SPICE Simulation Examples 1152

Summary 1158

Problems 1159

# 13 Signal Generators And Waveform-Shaping Circuits 1165

- 13.1 Basic Principles of Sinusoidal Oscillators 1166

- 13.1.1 The Oscillator Feedback Loop 1166

- 13.1.2 The Oscillation Criterion 1167

- 13.1.3 Nonlinear Amplitude Control 1168

- 13.1.4 A Popular Limiter Circuit for Amplitude Control 1169

- 13.2 Op Amp-RC Oscillator Circuits 1171

- 13.2.1 The Wien-Bridge Oscillator 1171

- 13.2.2 The Phase-Shift Oscillator 1174

- 13.2.3 The Quadrature Oscillator 1176

- 13.2.4 The Active-Filter-Tuned Oscillator 1177

- 13.2.5 A Final Remark 1179

- 13.3 LC and Crystal Oscillators 1179

- 13.3.1 LC-Tuned Oscillators 1179

- 13.3.2 Crystal Oscillators 1182

- 13.4 Bistable Multivibrators 1185

- 13.4.1 The Feedback Loop 1185

- 13.4.2 Transfer Characteristics of the Bistable Circuit 1186

- 13.4.3 Triggering the Bistable Circuit 1187

- 13.4.4 The Bistable Circuit as a Memory Element 1188

- 13.4.5 A Bistable Circuit with Noninverting Transfer Characteristics 1188

- 13.4.6 Application of the Bistable Circuit as a Comparator 1189

- 13.4.7 Making the Output Levels More Precise 1191

- 13.5 Generation of Square and Triangular Waveforms Using Astable Multivibrators 1192

- 13.5.1 Operation of the Astable Multivibrator 1192

13.5.2 Generation of Triangular Waveforms 1194

- 13.6 Generation of a Standardized Pulse—The Monostable Multivibrator 1196

- 13.7 Integrated-Circuit Timers 1198

- 13.7.1 The 555 Circuit 1198

- 13.7.2 Implementing a Monostable Multivibrator Using the 555 IC 1199

- 13.7.3 An Astable Multivibrator Using the 555 IC 1201

- 13.8 Nonlinear Waveform-Shaping Circuits 1203

- 13.8.1 The Breakpoint Method 1203

- 13.8.2 The Nonlinear-Amplification Method 1205

- 13.9 Precision Rectifier Circuits 1206

- 13.9.1 Precision Half-Wave Rectifier-The "Superdiode" 1207

- 13.9.2 An Alternative Circuit 1208

- 13.9.3 An Application: Measuring AC Voltages 1209

- 13.9.4 Precision Full-Wave Rectifier 1210

- 13.9.5 A Precision Bridge Rectifier for Instrumentation Applications 1212

- 13.9.6 Precision Peak Rectifiers 1213

- 13.9.7 A Buffered Precision Peak Detector 1213

- 13.9.8 A Precision Clamping Circuit 1214

- 13.10 SPICE Simulation Examples 1214

Summary 1219 Problems 1220

# 14 Output Stages and Power Amplifiers 1229

#### Introduction 1229

- 14.1 Classification of Output Stages 1230

- 14.2 Class A Output Stage 1231

- 14.2.1 Transfer Characteristic 1231

- 14.2.2 Signal Waveforms 1233

- 14.2.3 Power Dissipation 1233

- 14.2.4 Power-Conversion Efficiency 1235

- 14.3 Class B Output Stage 1235

- 14.3.1 Circuit Operation 1236

- 14.3.2 Transfer Characteristic 1236

- 14.3.3 Power-Conversion Efficiency 1236

- 14.3.4 Power Dissipation 1238

- 14.3.5 Reducing Crossover Distortion 1240

- 14.3.6 Single-Supply Operation 1240

- 14.4 Class AB Output Stage 1241

- 14.4.1 Circuit Operation 1242

- 14.4.2 Output Resistance 1243

- 14.5 Biasing the Class AB Circuit 1244

- Diasing the Class AB Circuit 124

- 14.5.1 Biasing Using Diodes 1244

- 14.5.2 Biasing Using the  $V_{BE}$  Multiplier 1246

- 14.6 Power BJTs 1249

- 14.6.1 Junction Temperature 1249

- 14.6.2 Thermal Resistance 1249

- 14.6.3 Power Dissipation Versus Temperature 1250

- 14.6.4 Transistor Case and Heat Sink 1251

- 14.6.5 The BJT Safe Operating Area 1254

- 14.6.6 Parameter Values of Power Transistors 1255

- 14.7 Variations on the Class AB Configuration 1256

- 14.7.1 Use of Input Emitter Followers 1256

- 14.7.2 Use of Compound Devices 1257

- 14.7.3 Short-Circuit Protection 1259

- 14.7.4 Thermal Shutdown 1260

- 14.8 IC Power Amplifiers 1261

- 14.8.1 A Fixed-Gain IC Power Amplifier 1261

- 14.8.2 Power Op Amps 1265

- 14.8.3 The Bridge Amplifier 1265

- 14.9 MOS Power Transistors 1266

- 14.9.1 Structure of the Power MOSFET 1266

- 14.9.2 Characteristics of Power MOSFETs 1268

- 14.9.3 Temperature Effects 1269

- 14.9.4 Comparison with BJTs 1269

- 14.9.5 A Class AB Output Stage Utilizing MOSFETs 1270

- 14.10 SPICE Simulation Example 1271

Summary 1276

Problems 1277

#### APPENDIXES

- A VLSI Fabrication Technology A-1

- B Two-Port Network Parameters B-1

- C Some Useful Network Theorems C-1

- D Single-Time-Constant Circuits D-1

- E s-Domain Analysis: Poles, Zeros, and Bode Plots E-1

- F Bibliography F-1

- G Standard Resistance Values and Unit Prefixes G-1

- H Answers to Selected Problems H-1

INDEX IN-1

Microelectronic Circuits, fifth edition, is intended as a text for the core courses in electronic circuits taught to majors in electrical and computer engineering. It should also prove useful to engineers and other professionals wishing to update their knowledge through self-study.

As was the case with the first four editions, the objective of this book is to develop in the reader the ability to analyze and design electronic circuits, both analog and digital, discrete and integrated. While the application of integrated circuits is covered, emphasis is placed on transistor circuit design. This is done because of our belief that even if the majority of those studying the book were not to pursue a career in IC design, knowledge of what is inside the IC package would enable intelligent and innovative application of such chips. Furthermore, with the advances in VLSI technology and design methodology, IC design itself is becoming accessible to an increasing number of engineers.

# **PREREQUISITES**

The prerequisite for studying the material in this book is a first course in circuit analysis. As a review, some linear circuits material is included here in appendixes: specifically, two-port network parameters in Appendix B; some useful network theorems in Appendix C; single-time-constant circuits in Appendix D; and s-domain analysis in Appendix E. No prior knowledge of physical electronics is assumed. All required device physics is included, and Appendix A provides a brief description of IC fabrication.

# NEW TO THIS EDITION

Although the philosophy and pedagogical approach of the first four editions have been retained, several changes have been made to both organization and coverage.

- 1. The book has been reorganized into three parts. Part I: Devices and Basic Circuits, composed of the first five chapters, provides a coherent and reasonably comprehensive single-semester introductory course in electronics. Similarly, Part II: Analog and Digital Integrated Circuits (Chapters 6–10) presents a body of material suitable for a second one-semester course. Finally, four carefully chosen subjects are included in Part III: Selected Topics. These can be used as enhancements or substitutions for some of the material in earlier chapters, as resources for projects or thesis work, and/or as part of a third course.

- 2. Each chapter is organized so that the essential "must-cover" topics are placed first, and the more specialized material appears last. This allows considerable flexibility in teaching and learning from the book.

- 3. Chapter 4, MOSFETs, and Chapter 5, BJTs, have been completely rewritten, updated, and made completely independent of each other. The MOSFET chapter is placed first to reflect the fact that it is currently the most significant electronics device by a wide margin. However, if desired, the BJT can be covered first. Also, the identical structure of the two chapters makes teaching and learning about the second device easier and faster.

xxiii

- PREFACE

- 4. To make the first course comprehensive, both Chapters 4 and 5 include material on amplifier and digital-logic circuits. In addition, the frequency response of the basic common-source (common-emitter) amplifier is included. This is important for students who might not take a second course in electronics.

- 5. A new chapter on integrated-circuit (IC) amplifiers (Chapter 6) is added. It begins with a comprehensive comparison between the MOSFET and the BJT. Typical parameter values of devices produced by modern submicron fabrication processes are given and utilized in the examples, exercises, and end-of-chapter problems. The study of each amplifier configuration includes its frequency response. This should make the study of amplifier frequency response more interesting and somewhat easier.

- 6. The material on differential and multistage amplifiers in Chapter 7 has been rewritten to present the MOSFET differential pair first. Here also, the examples, exercises, and problems have been expanded and updated to utilize parameter values representative of modern submicron technologies.

- 7. Throughout the book, greater emphasis is placed on MOSFET circuits.

- 8. To make room for new material, some of the topics that have become less current, such as JFETs and TTL, or have remained highly specialized, such as GaAs devices and circuits, have been removed from the book. However, they are made available on the CD accompanying the book and on the book's website.

- 9. As a study aid and for easy reference, many summary tables have been added.

- 10. The review exercises, examples, and end-of-chapter problems have been updated and their numbers and variety increased.

- 11. The SPICE sections have been rewritten and the SPICE examples now utilize schematic entry. To enable further experimentation, the files for all SPICE examples are provided on the CD and website.

# THE CD-ROM AND THE WEBSITE

A CD-ROM accompanies this book. It contains much useful supplementary information and material intended to enrich the student's learning experience. These include (1) A Student's Edition of OrCAD PSpice 9.2. (2) The input files for all the SPICE examples in this book. (3) A link to the book's website accessing PowerPoint slides of every figure in this book that students can print and carry to class to facilitate taking notes. (4) Bonus text material of specialized topics not covered in the current edition of the textbook. These include: JFETs, GaAs devices and circuits, and TTL circuits.

A website for the book has been set up (www.sedrasmith.org). Its content will change frequently to reflect new developments in the field. It features SPICE models and files for all PSpice examples, links to industrial and academic websites of interest, and a message center to communicate with the authors. There is also a link to the Higher Education Group of Oxford University Press so professors can receive complete text support.

# **EMPHASIS ON DESIGN**

It has been our philosophy that circuit design is best taught by pointing out the various tradeoffs available in selecting a circuit configuration and in selecting component values for a given configuration. The emphasis on design has been increased in this edition by including more design examples, exercise problems, and end-of-chapter problems. Those exercises and

end-of-chapter problems that are considered "design-oriented" are indicated with a D. Also, the most valuable design aid, SPICE, is utilized throughout the book, as already outlined.

# EXERCISES, END-OF-CHAPTER PROBLEMS, AND ADDITIONAL SOLVED PROBLEMS

Over 450 exercises are integrated throughout the text. The answer to each exercise is given below the exercise so students can check their understanding of the material as they read. Solving these exercises should enable the reader to gauge his or her grasp of the preceding material. In addition, more than 1370 end-of-chapter problems, about a third of which are new to this edition, are provided. The problems are keyed to the individual sections and their degree of difficulty is indicated by a rating system: difficult problems are marked with as asterisk (\*); more difficult problems with two asterisks (\*\*); and very difficult (and/or time consuming) problems with three asterisks (\*\*\*). We must admit, however, that this classification is by no means exact. Our rating no doubt had depended to some degree on our thinking (and mood!) at the time a particular problem was created. Answers to about half the problems are given in Appendix H. Complete solutions for all exercises and problems are included in the Instructor's Manual, which is available from the publisher for those instructors who adopt the book.

As in the previous four editions, many examples are included. The examples, and indeed most of the problems and exercises, are based on real circuits and anticipate the applications encountered in designing real-life circuits. This edition continues the use of numbered solution steps in the figures for many examples, as an attempt to recreate the dynamics of the classroom

A recurring request from many of the students who used earlier editions of the book has been for solved problems. To satisfy this need, a book of additional problems with solutions is available with this edition (see the list of available ancillaries later in this preface).

# AN OUTLINE FOR THE READER

The book starts with an introduction to the basic concepts of electronics in Chapter 1. Signals, their frequency spectra, and their analog and digital forms are presented. Amplifiers are introduced as circuit building blocks and their various types and models are studied. The basic element of digital electronics, the digital logic inverter, is defined in terms of its voltagetransfer characteristic, and its various implementations using voltage and current switches are discussed. This chapter also establishes some of the terminology and conventions used throughout the text.

The next four chapters are devoted to the study of electronic devices and basic circuits and constitute the bulk of Part I of the text. Chapter 2 deals with operational amplifiers, their terminal characteristics, simple applications, and limitations. We have chosen to discuss the op amp as a circuit building block at this early stage simply because it is easy to deal with and because the student can experiment with op-amp circuits that perform nontrivial tasks with relative ease and with a sense of accomplishment. We have found this approach to be highly motivating to the student. We should point out, however, that part or all of this chapter can be skipped and studied at a later stage (for instance in conjunction with Chapter 7, Chapter 8, and/or Chapter 9) with no loss of continuity.

Chapter 3 is devoted to the study of the most fundamental electronic device, the pn junction diode. The diode terminal characteristics and its hierarchy of models and basic circuit

applications are presented. To understand the physical operation of the diode, and indeed of the MOSFET and the BJT, a concise but substantial introduction to semiconductors and the pn junction is provided. This material is placed near the end of the chapter (Section 3.7) so that part or all of it can be skipped by those who have already had a course in physical electronics.

Chapters 4 and 5 deal with the two major electronic devices—the MOS field-effect transistor (MOSFET) and the bipolar junction transistor (BJT), respectively. The two chapters have an identical structure and are completely independent of each other and thus, can be covered in either order. Each chapter begins with a study of the device structure and its physical operation, leading to a description of its terminal characteristics. Then, to establish in the reader a high degree of familiarity with the operation of the transistor as a circuit element, a large number of examples are presented of dc circuits utilizing the device. The large-signal operation of the basic common-source (common-emitter) circuit is then studied and used to delineate the region over which the device can be used as a linear amplifier from those regions where it can be used as a switch. This makes clear the need for biasing the transistor and leads naturally to the study of biasing methods. At this point, the biasing methods used are mostly for discrete circuits, leaving the study of IC biasing to Chapter 6. Next, small-signal operation is studied and small-signal models are derived. This is followed by a study of the basic configurations of discrete-circuit amplifiers. The internal capacitive effects that limit the high-frequency operation of the transistor are then studied, and the high-frequency equivalent-circuit model is presented. This model is then used to determine the high-frequency response of a common-source (common-emitter) amplifier. As well, the low-frequency response resulting from the use of coupling and bypass capacitors is also presented. The basic digital-logic inverter circuit is then studied. Both chapters conclude with a study of the transistor models used in SPICE together with circuit-simulation examples using PSpice. This description should indicate that Chapters 4 and 5 contain the essential material for a first course in electronics.

Part II: Analog and Digital Integrated Circuits (Chapters 6-10) begins with a comprehensive compilation and comparison of the properties of the MOSFET and the BJT. The comparison is facilitated by the provision of typical parameter values of devices fabricated with modern process technologies. Following a study of biasing methods employed in IC amplifier design (Section 6.3), and some basic background material for the analysis of highfrequency amplifier response (Section 6.4), the various configurations of single-stage IC amplifiers are presented in a systematic manner. In each case, the MOS circuit is presented first. Some transistor-pair configurations that are usually treated as a single stage, such as the cascode and the Darlington circuits, are also studied. Each section includes a study of the high-frequency response of the particular amplifier configuration. Again, we believe that this "in-situ" study of frequency response is superior to the traditional approach of postponing all coverage of frequency response to a later chapter. As in other chapters, the more specialized material, including advanced current-mirror and current-source concepts, is placed in the second half of the chapter, allowing the reader to skip some of this material in a first reading. This chapter should provide an excellent preparation for an in-depth study of analog IC design.

The study of IC amplifiers is continued in Chapter 7 where the emphasis is on two major topics: differential amplifiers and multistage amplifiers. Here again, the MOSFET differential pair is treated first. Also, frequency response is discussed where needed, including in the two examples of multistage amplifiers.

Chapter 8 deals with the important topic of feedback. Practical circuit applications of negative feedback are presented. We also discuss the stability problem in feedback amplifiers and treat frequency compensation in some detail.

Chapter 9 integrates the material on analog IC design presented in the preceding three chapters and applies it to the analysis and design of two major analog IC functional blocks: op amps and data converters. Both CMOS and bipolar op amps are studied. The dataconverter sections provide a bridge to the study of digital CMOS logic circuits in Chapter 10.

Chapter 10 builds on the introduction to CMOS logic circuits in Section 4.10 and includes a carefully selected set of topics on static and dynamic CMOS logic circuits that round out the study of analog and digital ICs in Part II.

The study of digital circuits is continued in the first of the four selected-topics chapters that comprise Part III. Specifically, Chapter 11 deals with memory and related circuits, such as latches, flip-flops, and monostable and stable multivibrators. As well, two somewhat specialized but significant digital circuit technologies are studied; emitter-coupled logic (ECL) and BiCMOS. The two digital chapters (10 and 11) together with the earlier material on digital circuits should prepare the reader well for a subsequent course on digital IC design or VLSI circuits.

The next two chapters of Part III, Chapters 12 and 13, are application or system oriented. Chapter 12 is devoted to the study of analog-filter design and tuned amplifiers. Chapter 13 presents a study of sinusoidal oscillators, waveform generators, and other nonlinear signal-processing circuits.

The last chapter of the book, Chapter 14, deals with various types of amplifier output stages. Thermal design is studied, and examples of IC power amplifiers are presented.

The eight appendixes contain much useful background and supplementary material. We wish to draw the reader's attention in particular to Appendix A, which provides a concise introduction to the important topic of IC fabrication technology including IC layout.

# **COURSE ORGANIZATION**

The book contains sufficient material for a sequence of two single-semester courses (each of 40 to 50 lecture hours). The organization of the book provides considerable flexibility in course design. In the following, we suggest various possibilities for the two courses.

#### The First Course

The most obvious package for the first course consists of Chapters 1 through 5. However, if time is limited, some or all of the following sections can be postponed to the second course: 1.6, 1.7, 2.6, 2.7, 2.8, 3.6, 3.8, 4.8, 4.9, 4.10, 4.11, 5.8, 5.9, and 5.10. It is also quite possible to omit Chapter 2 altogether from this course. Also, it is possible to concentrate on the MOSFET (Chapter 4) and cover the BJT (Chapter 5) only partially and/or more quickly. Covering Chapter 5 thoroughly and Chapter 4 only partially and/or more quickly is also possible—but not recommended! An entirely analog first course is also possible by omitting Sections 1.7, 4.10, and 5.10. A digitally oriented first course is also possible. It would consist of the following sections; 1.1, 1.2, 1.3, 1.4, 1.7, 1.8, 3.1, 3.2, 3.3, 3.4, 3.7, 4.1, 4.2, 4.3, 4.4, 4.10, 4.12, 5.1, 5.2, 5.3, 5.4, 5.10, 5.11, all of Chapter 10, and selected topics from Chapter 11. Also, if time permits, some material from Chapter 2 on op amps would be beneficial.

# The Second Course

An excellent place to begin the second course is Chapter 6 where Section 6.2 can serve as a review of the MOSFET and BJT characteristics. Ideally, the second course would cover PREFACE

Chapters 6 through 10 (assuming, of course, that the first course covered Chapters 1 through 5). If time is short, either Chapter 10 can postponed to a subsequent course on digital circuits and/or some sections of Chapters 6-9 can be omitted. One possibility would be to deemphasize bipolar circuits by omitting some or all of the bipolar sections in Chapters 6, 7, and 9. Another would be to reduce somewhat the coverage of feedback (Chapter 8). Also, data converters can be easily deleted from the second course. Still, for Chapter 9, perhaps only CMOS op amps need to be covered and the 741 deleted or postponed. It is also possible to replace some of the material from Chapters 6-10 by selected topics from Chapters 11-14. For instance, in an entirely analog second course, Chapter 10 can be replaced by a selection of topics from Chapters 13-14.

# **ANCILLARIES**

A complete set of ancillary materials is available with this text to support your course.

# For the Instructor

The Instructor's Manual with Transparency Masters provides complete worked solutions to all the exercises in each chapter and all the end-of-chapter problems in the text. It also contains 200 transparency masters that duplicate the figures in the text most often used

A set of Transparency Acetates of the 200 most important figures in the book.

A PowerPoint CD with slides of every figure in the book and each corresponding caption.

# For the Student and the Instructor

The CD-ROM included with every new copy of the textbook contains SPICE input files, a Student Edition of OrCAD PSpice 9.2 Lite Edition, a link to the website featuring PowerPoint slides of the book's illustrations, and bonus topics.

Laboratory Explorations for Microelectronic Circuits, 5th edition, by Kenneth C. Smith (KC), contains laboratory experiments and instructions for the major topics studied in the text.

KC's Problems and Solutions for Microelectronic Circuits, 5th edition, by Kenneth C. Smith (KC), contains hundreds of additional study problems with complete solutions, for students who want more practice.

SPICE, 2nd edition, by Gordon Roberts of McGill University and Adel Sedra, provides a detailed treatment of SPICE and its application in the analysis and design of circuits of the type studied in this book.

# **ACKNOWLEDGMENTS**

Many of the changes in this fifth edition were made in response to feedback received from some of the instructors who adopted the fourth edition. We are grateful to all those who took the time to write to us. In addition, the following reviewers provided detailed commentary on the fourth edition and suggested many of the changes that we have incorporated in this revision. To all of them, we extend our sincere thanks: Maurice Aburdene, Bucknell University; Patrick L. Chapman, University of Illinois at Urbana-Champaign; Artice Davis, San Jose State University; Paul M. Furth, New Mexico State University; Roobik Gharabagi, St. Louis

University; Reza Hashemian, Northern Illinois University; Ward J. Helms, University of Washington; Hsiung Hsu, Ohio State University; Marian Kazimierczuk, Wright State University; Roger King, University of Toledo; Robert J. Krueger, University of Wisconsin-Milwaukee; Un-Ku Moon, Oregon State University; John A. Ringo, Washington State University; Zvi S. Roth, Florida Atlantic University; Mulukutla Sarma, Northeastern University; John Scalzo, Louisiana State University; Ali Sheikholeslami, University of Toronto: Pierre Schmidt, Florida International University; Charles Sullivan, Dartmouth College; Gregory M. Wierzba, Michigan State University; and Alex Zaslavsky, Brown University.

We are also grateful to the following colleagues and friends who have provided many helpful suggestions: Anthony Chan-Carusone, University of Toronto; Roman Genov, University of Toronto; David Johns, University of Toronto; Ken Martin, University of Toronto; Wai-Tung Ng, University of Toronto; Khoman Phang, University of Toronto; Gordon Roberts, McGill University; and Ali Sheikholeslami, University of Toronto.

We remain grateful to the reviewers of the four previous editions: Michael Bartz, University of Memphis; Roy H. Cornely, New Jersey Institute of Technology; Dale L. Critchlow, University of Vermont; Steven de Haas, California State University-Sacramento; Eby G. Friedman, University of Rochester; Rhett T. George, Jr., Duke University; Richard Hornsey, York University; Robert Irvine, California State University, Pamona; John Khoury, Columbia University; Steve Jantzi, Broadcom; Jacob B. Khurgin, The Johns Hopkins University; Joy Laskar, Georgia Institute of Technology; David Luke, University of New Brunswick; Bahram Nabet, Drexel University; Dipankar Nagchoudhuri, Indian Institute of Technology, Delhi, India; David Nairn, Analog Devices; Joseph H. Nevin, University of Cincinnati; Rabin Raut, Concordia University; Richard Schreier, Analog Devices; Dipankar Sengupta, Royal Melbourne Institute of Technology; Michael L. Simpson, University of Tennessee; Karl A. Spuhl, Washington University; Daniel van der Weide, University of

A number of individuals made significant contributions to this edition. Anas Hamoui of the University of Toronto played a key role in shaping both the organization and content of this edition. In addition, he wrote the SPICE sections. Olivier Trescases of the University of Toronto preformed the SPICE simulations, Richard Schreier of Analog Devices helped us locate the excellent cover photo. Wai-Tung Ng of the University of Toronto completely rewrote Appendix A. Gordon Roberts of McGill University gave us permission to use some of the examples from the book SPICE by Roberts and Sedra. Mandana Amiri, Karen Kozma, Shahriar Mirabbasi, Roberto Rosales, Jim Somers of Sonora Designworks, and John Wilson all helped significantly in preparing the student and instructor support materials. Jennifer Rodrigues typed all the revisions with skill and good humor and assisted with many of the logistics. Laura Fujino assisted in the preparation of the index, and perhaps more importantly, in keeping one of us (KCS) focused. To all of these friends and colleagues we say thank you.

The authors would like to thank Cadence Design Systems, Inc., for allowing Oxford University Press to distribute OrCad Family Release 9.2 Lite Edition software with this book. We are grateful to John Geen from Analog Devices for providing the cover photo and to Tom McElwee (from TWM Research).

A large number of people at Oxford University Press contributed to the development of this edition and its various ancillaries. We would like to specifically mention Barbara Wasserman, Liza Murphy, Mary Beth Jarrad, Mac Hawkins, Barbara Brown, Cathleen Bennett, Celeste Alexander, Chris Critelli, Eve Siegel, Mary Hopkins, Jeanne Ambrosio, Trent Haywood, Jennifer Slomack, Ned Escobar, Jim Brooks, Debbie Agee, Sylvia Parrish, Lee Rozakis, Kathleen Kelly, Sheridan Orr, and Kerry Cahill.

We wish to extend special thanks to our Publisher at Oxford University Press, Chris Rogers. We are also grateful to Scott Burns, Marketing and Sales Director, for his many excellent and creative ideas and for his friendship. We received a great deal of support and advice from our previous editor and friend, Peter Gordon. After Peter's departure, the leadership of the project has been most ably assumed by Danielle Christensen, our current editor. Elyse Dubin, Director of Editorial, Design, and Production, played a pivotal role in ensuring that the book would receive the greatest possible attention in the various stages of design and production.

If there is a single person at Oxford University Press that is responsible for this book coming out on time and looking so good, it is our Managing Editor, Karen Shapiro: She has been simply great, and we are deeply indebted to her. We also wish to thank our families for their support and understanding.

Adel S. Sedra Kenneth C. Smith

# MICROELECTRONIC CIRCUITS

# DEVICES AND BASIC CIRCUITS

CHAPTER 1

Introduction to Electronics 5

CHAPTER 2

Operational Amplifiers 63

CHAPTER 3 Diodes 139

CHAPTER 4

MOS Field-Effect Transistors (MOSFETs) 235

CHAPTER 5

Bipolar Junction Transistors (BJTs) 377

# INTRODUCTION

Part I, Devices and Basic Circuits, includes the most fundamental and essential topics for the study of electronic circuits. At the same time, it constitutes a complete package for a first course on the subject.

Besides silicon diodes and transistors, the basic electronic devices, the op amp is studied in Part I. Although not an electronic device in the most fundamental sense, the op amp is commercially available as an integrated circuit (IC) package and has well-defined terminal characteristics. Thus, despite the fact that the op amp's internal circuit is complex, typically incorporating 20 or more transistors, its almost-ideal terminal behavior makes it possible to treat the op amp as a circuit element and to use it in the design of powerful circuits, as we do in Chapter 2, without any knowledge of its internal construction. We should mention, however, that the study of op amps can be delayed to a later point, and Chapter 2 can be skipped with no loss of continuity.

The most basic silicon device is the diode. In addition to learning about diodes and a sample of their applications, Chapter 3 also introduces the general topic of device modeling for the purpose of circuit analysis and design. Also, Section 3.7 provides a substantial introduction to the physical operation of semiconductor devices. This subject is then continued in Section 4.1 for the MOSFET and in Section 5.1 for the BJT. Taken together, these three sections provide a physical background sufficient for the study of electronic circuits at the level presented in this book.

The heart of this book, and of any electronics course, is the study of the two transistor types in use today: the MOS field-effect transistor (MOSFET) in Chapter 4 and the bipolar junction transistor (BJT) in Chapter 5. These two chapters have been written to be completely independent of one another and thus can be studied in either desired order. Furthermore, the two chapters have the same structure, making it easier and faster to study the second device, as well as to draw comparisons between the two device types.

Chapter 1 provides both an introduction to the study of electronics and a number of important concepts for the study of amplifiers (Sections 1.4–1.6) and of digital circuits (Section 1.7).

Each of the five chapters concludes with a section on the use of SPICE simulation in circuit analysis and design. Of particular importance here are the device models employed by SPICE. Finally, note that as in most of the chapters of this book, the *must-know* material is placed near the beginning of a chapter while the *good-to-know* topics are placed in the latter part of the chapter. Some of this latter material can therefore be skipped in a first course and covered at a later time, when needed.

# Introduction to Electronics

|     | Introduction 5                   | 1.6 | Frequency Response of      |

|-----|----------------------------------|-----|----------------------------|

| 1.1 | Signals 6                        |     | Amplifiers 31              |

| 1.2 | Frequency Spectrum of            | 1.7 | Digital Logic Inverters 40 |

|     | Signals 7                        | 1.8 | Circuit Simulation Using   |

| 1.3 | Analog and Digital Signals 10    |     | SPICE 49                   |

| 1.4 | Amplifiers 13                    |     | Summary 50                 |

| 1.5 | Circuit Models for Amplifiers 23 |     | Problems 51                |

# INTRODUCTION

The subject of this book is modern electronics, a field that has come to be known as **microelectronics**. **Microelectronics** refers to the integrated-circuit (IC) technology that at the time of this writing is capable of producing circuits that contain millions of components in a small piece of silicon (known as a **silicon chip**) whose area is on the order of  $100 \text{ mm}^2$ . One such microelectronic circuit, for example, is a complete digital computer, which accordingly is known as a **microcomputer** or, more generally, a **microprocessor**.

In this book we shall study electronic devices that can be used singly (in the design of **discrete circuits**) or as components of an **integrated-circuit** (**IC**) chip. We shall study the design and analysis of interconnections of these devices, which form discrete and integrated circuits of varying complexity and perform a wide variety of functions. We shall also learn about available IC chips and their application in the design of electronic systems.

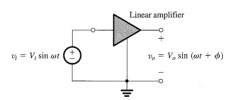

The purpose of this first chapter is to introduce some basic concepts and terminology. In particular, we shall learn about signals and about one of the most important signal-processing functions electronic circuits are designed to perform, namely, signal amplification. We shall then look at models for linear amplifiers. These models will be employed in subsequent chapters in the design and analysis of actual amplifier circuits.

Whereas the amplifier is the basic element of analog circuits, the logic inverter plays this role in digital circuits. We shall therefore take a preliminary look at the digital inverter, its circuit function, and important characteristics.

In addition to motivating the study of electronics, this chapter serves as a bridge between the study of linear circuits and that of the subject of this book: the design and analysis of electronic circuits.

# 1.1 SIGNALS

Signals contain information about a variety of things and activities in our physical world. Examples abound: Information about the weather is contained in signals that represent the air temperature, pressure, wind speed, etc. The voice of a radio announcer reading the news into a microphone provides an acoustic signal that contains information about world affairs. To monitor the status of a nuclear reactor, instruments are used to measure a multitude of relevant parameters, each instrument producing a signal.

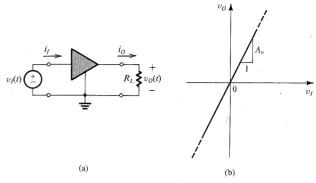

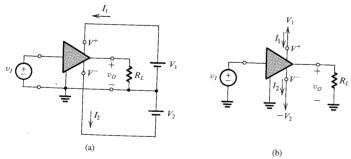

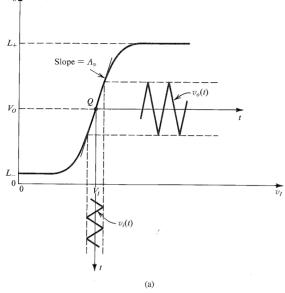

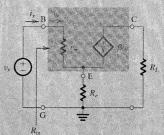

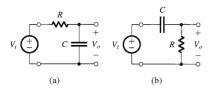

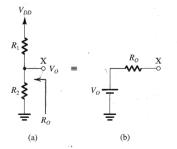

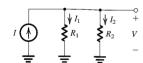

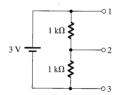

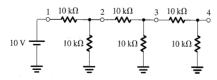

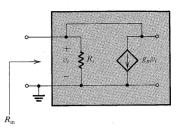

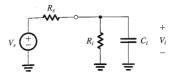

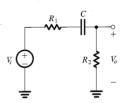

To extract required information from a set of signals, the observer (be it a human or a machine) invariably needs to process the signals in some predetermined manner. This signal processing is usually most conveniently performed by electronic systems. For this to be possible, however, the signal must first be converted into an electric signal, that is, a voltage or a current. This process is accomplished by devices known as transducers. A variety of transducers exist, each suitable for one of the various forms of physical signals. For instance, the sound waves generated by a human can be converted into electric signals using a microphone, which is in effect a pressure transducer. It is not our purpose here to study transducers; rather, we shall assume that the signals of interest already exist in the electrical domain and represent them by one of the two equivalent forms shown in Fig. 1.1. In Fig. 1.1(a) the signal is represented by a voltage source  $v_s(t)$  having a source resistance  $R_s$ . In the alternate representation of Fig. 1.1(b) the signal is represented by a current source  $i_s(t)$  having a source resistance  $R_s$ . Although the two representations are equivalent, that in Fig. 1.1(a) (known as the Thévenin form) is preferred when  $R_s$  is low. The representation of Fig. 1.1(b) (known as the Norton form) is preferred when  $R_s$  is high. The reader will come to appreciate this point later in this chapter when we study the different types of amplifiers. For the time being, it is important to be familiar with Thévenin's and Norton's theorems (for a brief review, see Appendix D) and to note that for the two representations in Fig. 1.1 to be equivalent, their parameters are related by

$$v_s(t) = R_s i_s(t)$$

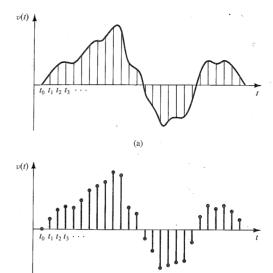

From the discussion above, it should be apparent that a signal is a time-varying quantity that can be represented by a graph such as that shown in Fig. 1.2. In fact, the information content of the signal is represented by the changes in its magnitude as time progresses; that is, the information is contained in the "wiggles" in the signal waveform. In general, such waveforms are difficult to characterize mathematically. In other words, it is not easy to describe succinctly an arbitrary-looking waveform such as that of Fig. 1.2. Of course, such a

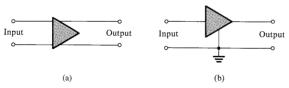

FIGURE 1.1 Two alternative representations of a signal source: (a) the Thévenin form, and (b) the Norton form

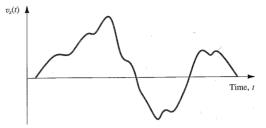

**FIGURE 1.2** An arbitrary voltage signal  $v_s(t)$ .

description is of great importance for the purpose of designing appropriate signal-processing circuits that perform desired functions on the given signal.

# **EXERCISES**

1.1 For the signal-source representations shown in Figs. 1.1(a) and 1.1(b), what are the open-circuit output voltages that would be observed? If, for each, the output terminals are short-circuited (i.e., wired together), what current would flow? For the representations to be equivalent, what must the relationship be between  $v_s$ ,  $i_s$ , and  $R_s$ ?

Ans. For (a),  $v_{cc} = v_{c}(t)$ ; for (b),  $v_{cc} = R_{s}i_{c}(t)$ ; for (a),  $i_{vc} = v_{c}(t)/R_{s}$ ; for (b),  $i_{sc} = i_{s}(t)$ ; for equivalency,  $v_s(t) = R_s i_s(t)$

1.2 A signal source has an open-circuit voltage of 10 mV and a short-circuit current of 10  $\mu$ A. What is the source resistance?

Ans. 1  $k\Omega$

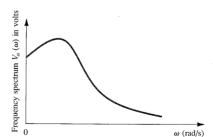

# 1.2 FREQUENCY SPECTRUM OF SIGNALS

An extremely useful characterization of a signal, and for that matter of any arbitrary function of time, is in terms of its frequency spectrum. Such a description of signals is obtained through the mathematical tools of Fourier series and Fourier transform. We are not interested at this point in the details of these transformations; suffice it to say that they provide the means for representing a voltage signal  $v_s(t)$  or a current signal  $i_s(t)$  as the sum of sine-wave signals of different frequencies and amplitudes. This makes the sine wave a very important signal in the analysis, design, and testing of electronic circuits. Therefore, we shall briefly review the properties of the sinusoid.

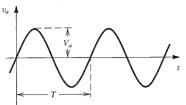

Figure 1.3 shows a sine-wave voltage signal  $v_a(t)$ ,

$$v_a(t) = V_a \sin \omega t \tag{1.1}$$

<sup>&</sup>lt;sup>1</sup> The reader who has not yet studied these topics should not be alarmed. No detailed application of this material will be made until Chapter 6, Nevertheless, a general understanding of Section 1.2 should be very helpful when studying early parts of this book.

**FIGURE 1.3** Sine-wave voltage signal of amplitude  $V_a$  and frequency f = 1/T Hz. The angular frequency  $\omega = 2\pi f$  rad/s.

where  $V_a$  denotes the peak value or amplitude in volts and  $\omega$  denotes the angular frequency in radians per second; that is,  $\omega=2\pi f$  rad/s, where f is the frequency in hertz, f=1/T Hz, and T is the period in seconds.

The sine-wave signal is completely characterized by its peak value  $V_a$ , its frequency  $\omega$ , and its phase with respect to an arbitrary reference time. In the case depicted in Fig. 1.3, the time origin has been chosen so that the phase angle is 0. It should be mentioned that it is common to express the amplitude of a sine-wave signal in terms of its root-mean-square (rms) value, which is equal to the peak value divided by  $\sqrt{2}$ . Thus the rms value of the sinusoid  $v_a(t)$  of Fig. 1.3 is  $V_a/\sqrt{2}$ . For instance, when we speak of the wall power supply in our homes as being 120 V, we mean that it has a sine waveform of  $120\sqrt{2}$  volts peak value.

Returning now to the representation of signals as the sum of sinusoids, we note that the Fourier series is utilized to accomplish this task for the special case when the signal is a periodic function of time. On the other hand, the Fourier transform is more general and can be used to obtain the frequency spectrum of a signal whose waveform is an arbitrary function of time.

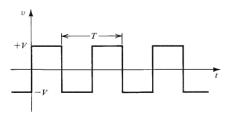

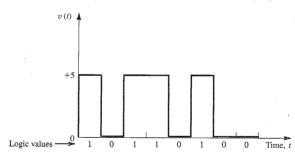

The Fourier series allows us to express a given periodic function of time as the sum of an infinite number of sinusoids whose frequencies are harmonically related. For instance, the symmetrical square-wave signal in Fig. 1.4 can be expressed as

$$v(t) = \frac{4V}{\pi} (\sin \omega_0 t + \frac{1}{3} \sin 3\omega_0 t + \frac{1}{5} \sin 5\omega_0 t + \cdots)$$

(1.2)

where V is the amplitude of the square wave and  $\omega_0 = 2\pi/T$  (T is the period of the square wave) is called the **fundamental frequency**. Note that because the amplitudes of the harmonics progressively decrease, the infinite series can be truncated, with the truncated series providing an approximation to the square waveform.

FIGURE 1.4 A symmetrical square-wave signal of amplitude V.

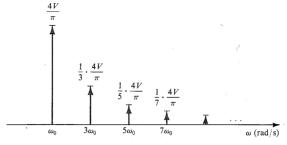

**FIGURE 1.5** The frequency spectrum (also known as the line spectrum) of the periodic square wave of Fig. 1.4.

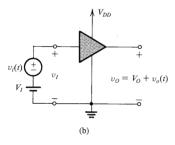

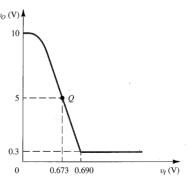

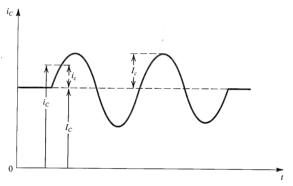

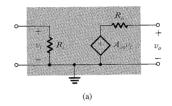

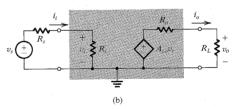

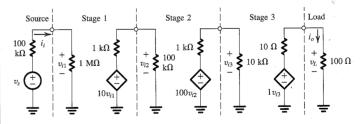

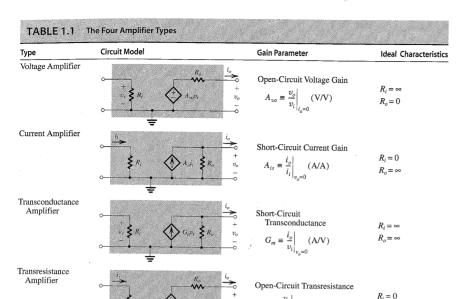

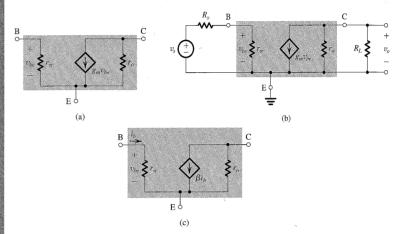

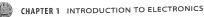

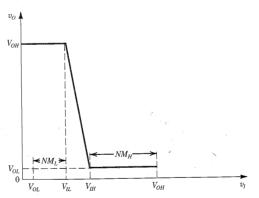

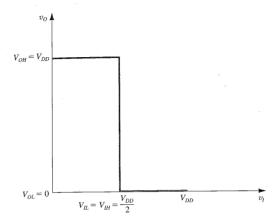

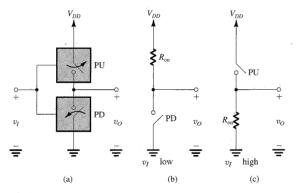

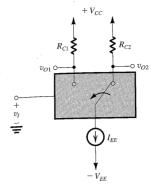

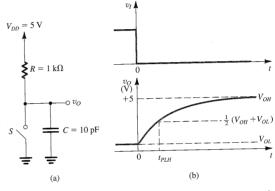

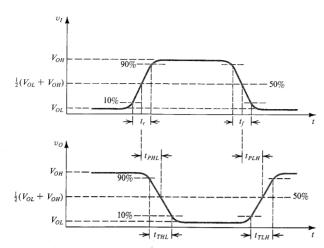

The sinusoidal components in the series of Eq. (1.2) constitute the frequency spectrum of the square-wave signal. Such a spectrum can be graphically represented as in Fig. 1.5, where the horizontal axis represents the angular frequency  $\omega$  in radians per second.