<u>\_\_\_\_</u>

- problem most economically? value should she connect to which node to solve her design driving stage have at node A? At node B? What capacitor input resistance of 100 kΩ, what output resistance must the respectively. If she knows that each amplifier stage has an ing the 3-dB frequency from 2 MHz to 150 kHz and 15 kHz, a capacitor of 1 nF, first to node A and then to node B, lowerthird stage, to ground with a small capacitor. While measurfrequency of a three-stage amplifier to 10 kHz considers **D\*1.74** A designer wishing to lower the overall upper 3-dB ing the overall frequency response of the amplifier, she shunts between the output of the second stage and the input of the the first stage and the input of the second stage, and Node B, shunting one of two nodes: Node A, between the output of

- find an expression for  $T(s) = V_o(s)/V_s(s)$ . amplifier has an open-circuit voltage gain  $(A_{\nu\rho})$  of 100 V/V/ corner frequencies result? For the situation in which the basic quency associated with each is less than 100 Hz? What actual the smallest capacitors needed to ensure that the corner frevalues only of the form  $1 \times 10^{-n}$  F. What are the values of to a 10-kΩ source and a 1-kΩ load. Available capacitors have and an output resistance of 1 kO is to be capacitor-coupled D1.75 An amplifier with an input resistance of 100 kΩ

- \*1.76 A voltage amplifier has the transfer function

$$L_{v} = \frac{100}{\left(1 + j\frac{f}{10^{4}}\right)\left(1 + \frac{10^{2}}{jf}\right)}$$

width of the amplifier (defined as the frequency range over Using the Bode plots for low-pass and high-pass STC netwhich the gain remains within 3 dB of the maximum value). works (Figs. 1.23 and 1.24), sketch a Bode plot for IA, J. Give 10° Hz, 10° Hz, 10° Hz, 10° Hz, and 10° Hz. Find the bandapproximate values for the gain magnitude at f = 10 Hz,  $10^2 \text{ Hz}$ ,

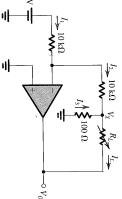

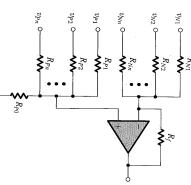

$T_i(s) = V_i(s)/V_s(s)$  and the corresponding cutoff (corner) \*1.77 For the circuit shown in Fig. P1.77 first, evaluate

> bandwidth between 3-dB cutoff points? Provide a Bode magnitude plot for  $|T(j\omega)|$ . What is the to form the overall transfer function,  $T(s) = T_i(s) \times T_o(s)$ . tions in the standard form (see Table 1.2), and combine them corresponding cutoff frequency. Put each of the transfer funcfrequency. Second, evaluate  $T_o(s) = V_o(s)/V_i(s)$  and the

- to meet the following design constraints: specify the values of the amplifier parameters  $R_i$ ,  $G_m$ , and  $R_c$ tance  $C_L$ . For given values of  $R_s$ ,  $R_L$ , and  $C_L$ , it is required to load consisting of a resistance  $R_L$  in parallel with a capacihaving a source resistance  $R_s$ , and its output is connected to a lent circuit shown in Table 1.1 is fed with a voltage source  $V_s$ D\*\*1.78 A transconductance amplifier having the equiva-

- than a specified value  $f_{3 dB}$ . (a) At most, x% of the input signal is lost in coupling the sig-(b) The 3-dB frequency of the amplifier is equal to or greater nal source to the amplifier (i.e.,  $V_i \ge [1 - (x/100)]V_s$ ).

- (c) The dc gain  $V_o/V_s$  is equal to or greater than a specified

Show that these constraints can be met by selecting

$$R_{i} \ge \left(\frac{100}{x} - 1\right) R_{s}$$

$$R_{o} \le \frac{1}{2\pi f_{3dB} C_{L} - (1/R_{L})}$$

$$G_{m} \ge \frac{A_{0} / [1 - (x / 100)]}{(R_{L} \parallel R_{o})}$$

$R_L = 10 \text{ k}\Omega$ ,  $C_L = 10 \text{ pF}$ , and  $f_{3dB} = 3 \text{ MHz}$ . Find  $R_{p}$ ,  $R_{o}$ , and  $G_{m}$  for  $R_{s} = 10 \text{ k}\Omega$ , x = 20%,  $A_{0} = 80$ ,

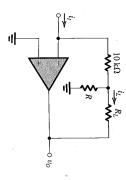

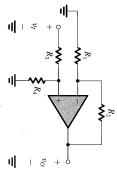

circuit is called a compensated attenuator and is frequently the condition  $C_1R_1 = C_2R_2$  applies. Under this condition the the transfer function can be made independent of frequency if function  $V_o(s)/V_i(s)$  of the circuit in Fig. P1.79. Show that \*1.79 Use the voltage-divider rule to find the transfer

FIGURE P1.77

employed in the design of oscilloscope probes. Find the transmission of the compensated attenuator in terms of  $R_1$  and  $R_2$ .

FIGURE P1.79

drop in gain is 3 dB? amplifier bandwidth? What are the frequencies at which the the maximum gain) at the two frequencies that define the cuits to be? What is the drop in gain in decibels (relative to What do you expect the corner frequencies of these two cirresponse of a high-pass STC circuit and that at the highthe gain falloff at the low-frequency end is determined by the tude no greater than 11.4° over the amplifier bandwidth, shown in Fig. 1.21 is specified to have a phase shift of magnifrequency end it is determined by a low-pass STC circuit. which extends from 100 Hz to 1 kHz. It has been found that \*1.80 An amplifier with a frequency response of the type

## SECTION 1.7: DIGITAL LOGIC INVERTERS

- noise margins,  $NM_H$  and  $NM_L$ .  $V_{IH} = 1.7 \text{ V}$ ,  $V_{OL} = 0 \text{ V}$ , and  $V_{OH} = 3.3 \text{ V}$ . Find the high and low **1.81** A particular logic inverter is specified to have  $V_L = 1.3 \text{ V}$ ,

- 0.5 V, and  $V_{OH} = 4$  V, find: 1.82 The voltage-transfer characteristic of a particular logic manner shown in Fig. 1.29. If  $V_L = 1.5 \text{ V}$ ,  $V_{IH} = 2.5 \text{ V}$ ,  $V_{OL} =$ inverter is modeled by three straight-line segments in the

- (a) The noise margins

- (b) The value of  $v_l$  at which  $v_O = v_l$  (known as the **inverter**

- (c) The voltage gain in the transition region

- value of  $V_{DD}$  is required? transition region? For a minimum noise margin of 1 V, what  $0.6 V_{DD}$ . What are the noise margins? What is the width of the 1.83 For a particular inverter design using a power supply  $V_{DD}$ ,  $V_{OL} = 0.1 V_{DD}$ ,  $V_{OH} = 0.8 V_{DD}$ ,  $V_{IL} = 0.4 V_{DD}$ , and  $V_{IH} = 0.00 V_{DD}$

- scale integrated (SSI) and medium-scale-integrated (MSI) other building blocks are available commercially in small-1.84 A logic circuit family that used to be very popular is boards to implement a digital system. The device data sheets packages. Such packages can be assembled on printed-circuit Transistor-Transistor Logic (TTL). The TTL logic gates and

(of the SN7400 type): provide the following specifications of the basic TTL inverter

- Logic-1 input level required to ensure a logic-0 level at the output: MIN (minimum) 2 V

- Logic-0 input level required to ensure a logic-1 level at the output: MAX (maximum) 0.8 V

- Propagation delay time to logic-0 level ( $t_{PHL}$ ): TYP 7 ns, Logic-1-level supply current: TYP 1 mA, MAX 2 mA Logic-0-level supply current: TYP 3 mA, MAX 5 mA Logic-0 output voltage: TYP 0.22 V, MAX 0.4 V Logic-1 output voltage: MIN 2.4 V, TYP (typical) 3.3 V

- Propagation delay time to logic-1 level ( $t_{PLH}$ ): TYP 11 ns, MAX 22 ns

MAX 15 ns

- (d) Find the propagation delay t<sub>p</sub>. to estimate the dynamic power dissipation. and is switched at a 1-MHz rate, use the formula in Eq. (1.28) (c) Assuming that the inverter drives a capacitance C<sub>L</sub> = 45 pF power dissipation in a typical circuit. The power supply is 5 V. time and in the 0-state 50% of the time, find the average static (b) Assuming that the inverter is in the 1-state 50% of the (a) Find the worst-case values of the noise margins

- 1.85 Consider an inverter implemented as in Fig. 1.31(a). Let  $V_{DD} = 5 \text{ V}, R = 2 \text{ k}\Omega, V_{\text{offset}} = 0.1 \text{ V}, R_{\text{on}} = 200 \Omega, V_{IL} = 1 \text{ V}, \text{ and}$

- (a) Find  $V_{OL}$ ,  $V_{OH}$ ,  $NM_H$ , and  $NM_L$ .

- is still providing an  $NM_H$  value at least equal to its  $NM_L$ the driving inverter, find the resulting value of  $V_{OH}$  and of of the fan-out inverters will have to be supplied through R of when the input voltage is low. Noting that the input currents is specified to require an input current of 0.2 mA when the load inverters, or fan-out inverters as they are usually called, Hence find the maximum value N can have while the inverter input voltage (of the fan-out inverter) is high and zero current (b) The inverter is driving N identical inverters. Each of these  $NM_H$  as a function of the number of fan-out inverters N.

- (c) Find the static power dissipation in the inverter in the two driving the maximum fan-out found in (b). cases: (i) the output is low, and (ii) the output is high and

- and  $V_{IL} = V_{IH} = V_{DD}/2$ . ment of Fig. 1.32 with switches having  $R_{\text{on}} = 1 \text{ k}\Omega$ ,  $V_{DD} = 5 \text{ V}$ , 1.86 A logic inverter is implemented using the arrange-

- (a) Find V<sub>OL</sub>, V<sub>OH</sub>, NM<sub>L</sub>, and NM<sub>H</sub>.

- $(t_{PHL})$  for C = 1 pF. Also find  $t_{THL}$  (see Fig. 1.35) and ground. Hence find the high-to-low propagation delay that a capacitance C is connected between the output node opens, and PD closes—find an expression for  $v_0(t)$  assuming (b) If  $v_l$  rises instantaneously from 0 V to +5 V and assuming the switches operate instantaneously—that is, at t = 0, PU

PROBLEMS

is -3.020 V, what is likely to be the actual gain of the amplifier? positive input to be? If the measured voltage at the positive input amplifier to be ideal, what would you expect the voltage at the -2.000 V and that at the negative input to be -3.000 V. For the

surements that were accidentally omitted (the blank entries). show the gain to be? Using this value, predict values of the meain view of the possibility of experimental error? What do they below. Are the results consistent? If not, are they reasonable, except for having a finite gain A. The results are tabulated 2.4 A set of experiments are run on an op amp that is ideal

| 7 6           | 5             | 3 2          | ъ.   | Experiment #          |

|---------------|---------------|--------------|------|-----------------------|

| 1.99<br>5.10  | 1.00<br>2.01  | 1.00         | 0.00 | 7                     |

| 2.00          | 1.10<br>2.00  | 1.00         | 0.00 | <b>V</b> <sub>2</sub> |

| 1.00<br>-5.10 | 10.1<br>-0.99 | 0.00<br>1.00 | 0.00 | <b>v</b> <sub>o</sub> |

- open-loop gain A. For  $G_m = 100 \text{ mA/V}$  and  $R_m = 10^{\circ} \Omega$ , what to model the internal structure of a particular op amp using tive internal structure for the op amp. In particular, we wish 2.5 Refer to Exercise 2.3. This problem explores an alternavalue of A results? tances  $G_m$  and a transresistance  $R_m$ , find an expression for the fier. Suggest an appropriate topology. For equal transconductwo transconductance amplifiers and one transresistance ampli-

- transducer pick up an interference signal that is a 60-Hz, 1-V 2.6 The two wires leading from the output terminals of a

system ground. for  $v_{cm}$ ,  $v_d$ , and the total signal between each wire and the 10-mV amplitude and 1000-Hz frequency. Give expressions sinusoid. The output signal of the transducer is sinusoidal of

the output voltage of the op amp can be expressed as input signals (refer to Fig. 2.4 for signal representation). Thus both the differential and common-mode components of their 2.7 Nonideal (i.e., real) operational amplifiers respond to

$$v_O = A_d v_{Id} + A_{cm} v_{Icm}$$

mode signals is measured by its CMRR, defined as in the text). The op amp's effectiveness in rejecting commontext) and  $A_{cm}$  is the common-mode gain (assumed to be zero where  $A_d$  is the differential gain (referred to simply as A in the

$$CMRR = 20 \log \left| \frac{A_d}{A_{cm}} \right|$$

Consider an op amp whose internal structure is of the type shown in Fig. E2.3 except for a mismatch  $\Delta G_m$  between the transconductances of the two channels; that is,

$$G_{m1} = G_m - \frac{1}{2}\Delta G_m$$

$$G_{m2} = G_m + \frac{1}{2}\Delta G_m$$

each other, calculate  $A_{cm}$  and CMRR the two transconductances are matched to within 0.1% of Find expressions for  $A_d$ ,  $A_{cm}$ , and CMRR. If  $A_d$  is 80 dB and

# SECTION 2.2: THE INVERTING CONFIGURATION

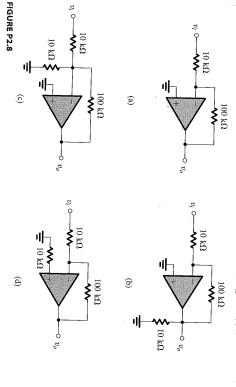

input resistance  $R_{in}$  of each of the circuits in Fig. P2.8 **2.8** Assuming ideal op amps, find the voltage gain  $v_o/v_i$  and

- $(1 \pm 0.05)$  times the nominal value, what range of outputs expect? If a dc voltage of +5.00 V is applied at the input, cisely 5.00 V? would you expect to actually measure for an input of pre-"5% resistors," having values somewhere in the range what output result? If the 10-kΩ resistors are said to be two 10-kΩ resistors. What closed-loop gain would you 2.9 A particular inverting circuit uses an ideal op amp and

- 2.10 You are provided with an ideal op amp and three 10-kΩ the input resistances in these two cases? gain? What is the smallest (nonzero) available gain? What are possible? What is the largest (noninfinite) available voltage many different inverting-amplifier circuit topologies are resistors. Using series and parallel resistor combinations, how

- results? networks in the inverting configuration, what closed-loop gain 2.11 For ideal op amps operating with the following feedback

(a)

$$R_1 = 10 \text{ k}\Omega$$

,  $R_2 = 10 \text{ k}\Omega$

(b)

$$R_1 = 10 \text{ k}\Omega, R_2 = 100 \text{ k}\Omega$$

(c)

$$R_1 = 10 \text{ k}\Omega, R_2 = 1 \text{ k}\Omega$$

(d)

$$R_1 = 100 \text{ k}\Omega$$

,  $R_2 = 10 \text{ M}\Omega$

(e)  $R_1 = 100 \text{ k}\Omega$ ,  $R_2 = 1 \text{ M}\Omega$

**p2.12** Using an ideal op amp, what are the values of the resistors

$$R_1$$

and  $R_2$  to be used to design amplifiers with the closed-loop gains listed below? In your designs, use at least one  $10-k\Omega$  resistor and another larger resistor.

- gain is -5 V/V and the total resistance used is 120 k $\Omega$ . D2.13 Design an inverting op-amp circuit for which the

- is the input resistance of your design? straint of having to use resistors no larger than 10 M $\Omega$ . What having the largest possible input resistance under the conop amp, design an inverting amplifier with a gain of 26 dB D2.14 Using the circuit of Fig. 2.5 and assuming an ideal

- What is its lowest value? Sketch and clearly label the waveform of the resulting output wave signal with levels of 0 V and 1 V is applied at the input. text with  $R_1 = 10 \text{ k}\Omega$  and  $R_2 = 100 \text{ k}\Omega$ . A symmetrical squarevoltage. What is its average value? What is its highest value? 2.15 An ideal op amp connected as shown in Fig. 2.5 of the

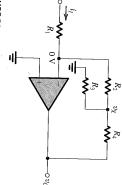

- tional current come from? drawn from the input signal source, where does the addicurrent supplied by the op amp is greater than the current through all branches and the voltages at all nodes. Since the 2.16 For the circuit in Fig. P2.16, find the currents

2 k5

FIGURE P2.16

- expected from such a circuit? resistance can deviate from the nominal value by as much as resistors  $R_1$  and  $R_2$  having x% tolerance (i.e., the value of each gain is -100 V/V and x = 5, what is the range of gain values Assume the op amp to be ideal. If the nominal closed-loop  $\pm x\%$ ). What is the tolerance on the realized closed-loop gain? 2.17 An inverting op amp circuit is fabricated with the

- the output voltages that might be found? ±1%, what are the limits of the output voltage produced? If actual values are the range bounded by the nominal value resistor? If these resistors are so-called 1% resistors, whose the -15-V supply can also vary by  $\pm 1\%$ , what is the range of the circuit. What are the voltages at the ends of the 5-kQ used to create a +5-V supply from a -15-V reference. Sketch 2.18 An ideal op amp with 5-kΩ and 15-kΩ resistors is

- resistor connected to the input be shunted to achieved this the smaller be adjusted? With what resistor must a 2-kΩ  $R_b$  when  $R_b$  is placed in parallel with  $R_a$ .) goal? (Note that a resistor  $R_a$  is said to be shunted by resistor 200 V/V. If the larger resistor used is 100 kΩ, to what must gain is -50 V/V uses an op amp whose open-loop gain is only 2.19 An inverting op-amp circuit for which the required

- gain of -100 V/V and an input resistance of 1 kΩ. **D2.20** (a) Design an inverting amplifier with a closed-loop

- values)? of your circuit to be (assuming the resistors have precise of 1000 V/V, what do you expect the closed-loop gain (b) If the op amp is known to have an open-loop gain

- (shunt) with  $R_1$  to restore the closed-loop gain to its nominal (c) Give the value of a resistor you can place in parallel Appendix G) value. Use the closest standard 1% resistor value (see

- output voltage ranges from  $-10~\mathrm{V}$  to  $+10~\mathrm{V}$ , what is the maximum voltage by which the "virtual ground node" departs used in the inverting configuration. If in this application the from its ideal value? 2.21 An op amp with an open-loop gain of 1000 V/V is

- **2.22** The circuit in Fig. P2.22 is frequently used to provide input resistance  $R_i \equiv v_i/i_i$  for the following cases: Derive expressions for the transresistance  $R_m \equiv v_o/i_i$  and the an output voltage  $v_o$  proportional to an input signal current  $i_i$ .

- (b) A is finite. (a) A is infinite.

#### FIGURE P2.22

- open-loop gain A of the op amp. 2.23 Derive an expression for the input resistance of the inverting amplifier of Fig. 2.5 taking into account the finite

- \*2.24 For an inverting op amp with open-loop gain A and the gain A must have (in terms of  $R_2/R_1$ ) for a gain error of nominal closed-loop gain  $R_2/R_1$ , find the minimum value

- compensation is achieved when  $R_c$  is selected according to finite A, a resistor  $R_c$  is shunted across  $R_1$ . Show that perfect inverting amplifier whose gain has a nominal magnitude for having a finite open-loop gain and is used to realize an \*2.25 Figure P2.25 shows an op amp that is ideal except 0.1%, 1%, and 10%. In each case, what value of resistor  $R_{1a}$  $G = R_2/R_1$ . To compensate for the gain reduction due to the can be used to shunt  $R_1$  to achieve the nominal result?

$$\frac{R_c}{R_1} = \frac{A - G}{1 + G}$$

#### FIGURE P2.25

- gain A required to realize a specified closed-loop gain \*2.26 Rearrange Eq. (2.5) to give the amplifier open-loop  $(G_{\rm nominal} = -R_2/R_1)$  within a specified gain error  $\varepsilon,$

- $G_{\text{nominal}}$

what is the minimum A required? For a closed-loop gain of -100 and a gain error of ≤10%,

- and k is 100. case in which the nominal closed-loop gain is 100, x is 50, in |G| by (x/k)%. Find the value of A required for the which a reduction of A by x% results in a reduction \*2.27 Using Eq. (2.5), determine the value of A for

- and assume the op amp to be ideal. Find values for  $R_3$  to obtain the following gains: **2.28** Consider the circuit in Fig. 2.8 with  $R_1 = R_2 = R_4 = 1 \text{ M}\Omega$ ,

- (a) -10 V/V

- (c) -2 V/V (b) -100 V/V

- must be designed to have a gain of -1000 V/V using resistors **D2.29** An inverting op-amp circuit using an ideal op amp no larger than 100 kΩ.

- (a) For the simple two-resistor circuit, what input resistance

- value of the smallest resistor needed? (b) If the circuit in Fig. 2.8 is used with three resistors of maximum value, what input resistance results? What is the

- gain  $(v_O/v_I)$  by first finding  $(v_X/v_I)$  and  $(v_O/v_X)$ . terminal). Use this observation to derive an expression for the the ideal op amp forces a virtual ground at the inverting input observation that  $R_2$  and  $R_3$  in effect are in parallel (because back is redrawn in Fig. P2.30 in a way that emphasizes the 2.30 The inverting circuit with the T network in the feed-

#### FIGURE P2.30

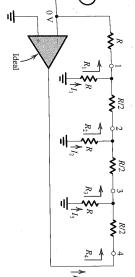

- sion of the circuit in Fig. 2.8. \*2.31 The circuit in Fig. P2.31 can be considered an exten-

- (b) Find the currents  $I_1$ ,  $I_2$ ,  $I_3$ , and  $I_4$  in terms of the input (a) Find the resistances looking into node 1,  $R_1$ ; node 2,  $R_2$ ; node 3,  $R_3$ ; and node 4,  $R_4$

#### FIGURE P2.31

- and  $V_4$  in terms of (IR). (c) Find the voltages at nodes 1, 2, 3, and 4, that is,  $V_1$ ,  $V_2$ ,  $V_3$ ,

- 2.32 The circuit in Fig. P2.32 utilizes an ideal op amp.

- (a) Find I<sub>1</sub>, I<sub>2</sub>, I<sub>3</sub>, and V<sub>3</sub>

- allowed value for  $R_L$ (b) If  $V_0$  is not to be lower than -13 V, find the maximum

- (c) If  $R_L$  is varied in the range 100  $\Omega$  to 1 k $\Omega$ , what is the corresponding change in  $I_L$  and in  $V_O$ ?

#### FIGURE P2.32

**D2.33** Assuming the op amp to be ideal, it is required to design the circuit shown in Fig. P2.33 to implement a current amplifier with gain  $i_L/i_I = 20 \text{ A/A}$ .

FIGURE P2.33

- (a) Find the required value for R.

- 1 mA and a source resistance of 10 k $\Omega$ , find  $i_L$ . (c) What is the input resistance of the current amplifier? If long as  $v_0$  is in the range  $\pm 12$  V. What range of  $i_I$  is possible? (b) If  $R_L = 1 \text{ k}\Omega$  and the op amp operates in an ideal manner so the amplifier is fed with a current source having a current of

- 2.34 Figure P2.34 shows the inverting amplifier circuit of divider is composed of  $R_4$  and  $(R_3 \parallel R_2)$ . that  $R_2$  appears in effect across  $R_3$  and, thus, that the voltage ple 2.2. Show that the exact result can be obtained by noting manipulation, compare it with the result obtained in Examand thus that the loading of the feedback network can be able at node A) is fed back through  $R_2$ . Assuming  $R_2 \gg R_3$ and from which a fraction of the output voltage (that availthought of as a voltage divider connected across the output  $v_0$ Fig. 2.8 redrawn to emphasize the fact that  $R_3$  and  $R_4$  can be imate) relationship between  $v_0$  and  $v_t$ . With appropriate function of  $v_i$ . Use these two relationships to find the (approxignored, express  $v_A$  as a function of  $v_O$ . Now express  $v_A$  as a

FIGURE P2.34

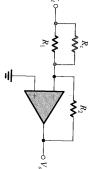

-1 V/V to -10 V/V using the 10-k $\Omega$  potentiometer  $R_4$ . What input resistance of 100 k $\!\Omega$  and a gain that can be varied from D2.35 Design the circuit shown in Fig. P2.35 to have an

its middle value? voltage gain results when the potentiometer is set exactly at

#### FIGURE P2.35

- signal  $v_2$  is connected to the third. Express  $v_0$  in terms of  $v_1$ 50 k $\Omega$ . A signal  $v_1$  is connected to two of the inputs while a and  $v_2$ . If  $v_1 = 3$  V and  $v_2 = -3$  V, what is  $v_0$ ? three inputs using 100-k $\Omega$  resistors and a feedback resistor of 2.36 A weighted summer circuit using an ideal op amp has

- tors but ones for which the input current (from each input D2.37 Design an op amp circuit to provide an output signal source) does not exceed 0.1 mA for 1-V input signals.  $v_0 = -[4v_1 + (v_2/3)]$ . Choose relatively low values of resis-

- than 10 kΩ. op-amp circuit with inputs  $v_1$ ,  $v_2$ , and  $v_3$  whose output is **D2.38** Using the scheme illustrated in Fig. 2.10, design an  $v_0 = -(2v_1 + 4v_2 + 8v_3)$  using small resistors but no smaller

- **D2.39** An ideal op amp is connected in the weighted summer configuration of Fig. 2.10. The feedback resistor  $R_f$ implement the following functions: circuit configurations, how this basic circuit can be used to input terminal of the op amp. Show, by sketching the various 10 k $\Omega$ , and six 10-k $\Omega$  resistors are connected to the inverting

- (a)  $v_0 = -(v_1 + 2v_2 + 3v_3)$

- (b)  $v_0 = -(v_1 + v_2 + 2v_3 + 2v_4)$

- (c)  $v_0 = -(v_1 + 5v_2)$

- (d)  $v_0 = -6v_1$

circuit. How would you realize a summing coefficient that additional summing functions that you can realize with this nal sources supplying  $v_1$ ,  $v_2$ ,  $v_3$ , and  $v_4$ . Suggest at least two In each case find the input resistance seen by each of the sig-

available. Sketch the output signal waveform. to the sine-wave signal you have a dc reference voltage of 2  $\rm V$ nal of  $5 \sin(\omega t)$  V from zero to -5 V. Assume that in addition a weighted summer that shifts the dc level of a sine-wave sig-**D2.40** Give a circuit, complete with component values, for

> D2.41 Use two ideal op amps and resistors to implement the summing function.

$$v_0 = v_1 + 2v_2 - 3v_3 - 4v_4$$

- overall gain of 10 as well. The op amps available are ideal D\*2.42 In an instrumentation system, there is a need to except that their output voltage swing is limited to  $\pm 10 \text{ V}$ . 1000-Hz component in the process, arrange to provide an mainly 10-kΩ resistors. Since it is desirable to amplify the that finds the required difference using two op amps and  $3\sin(2\pi\times60t) - 0.01\sin(2\pi\times1000t)$  volts. Draw a circuit 60t) + 0.01 sin( $2\pi \times 1000t$ ), volts and another of  $v_2$  = take the difference between two signals, one of  $v_1 = 3 \sin(2\pi \times 1)$

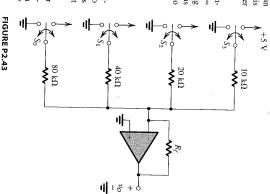

- to ground, while if  $a_2$  is 1 then  $S_2$  connects the 20-k $\Omega$  resistor to the +5-V power supply. Show that  $v_0$  is given by instance, if  $a_2$  is 0 then switch  $S_2$  connects the 20-k $\Omega$  resistor word controls the correspondingly numbered switch. For to the value of the digital input. Each of the bits of the input converter (DAC). The circuit accepts a 4-bit input binary \*2.43 Figure P2.43 shows a circuit for a digital-to-analog 1, and it provides an analog output voltage  $v_0$  proportional word  $a_3a_2a_1a_0$ , where  $a_0$ ,  $a_1$ ,  $a_2$ , and  $a_3$  take the values of 0 or

$$v_{o} = -\frac{R_{f}}{16} [2^{0}a_{0} + 2^{1}a_{1} + 2^{2}a_{2} + 2^{3}a_{3}]$$

0 to -12 volts. where  $R_f$  is in k $\Omega$ . Find the value of  $R_f$  so that  $v_O$  ranges from

### CONFIGURATION SECTION 2.3: THE NONINVERTING

- **D2.44** Using an ideal op amp to implement designs for the following closed-loop gains, what values of resistors  $(R_1, R_2)$ tor as the smallest resistor in your design. should be used? Where possible, use at least one 10-k\O resis-

- (a) +1 V/V (b) +2 V/V

- (d) +100 V/V (c) +101 V/V

- or +2.0 V/V simply by short-circuiting a single resistor in these can be easily converted to have a gain of either +1.0 V/V inverting amplifier to obtain a gain of +1.5 V/V, using only **D2.45** Design a circuit based on the topology of the noneach case? 10-k $\Omega$  resistors. Note that there are two possibilities. Which of

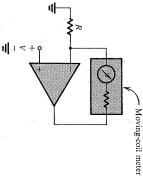

- calibration? the value of R such that full-scale reading is obtained when V deflection when the current passing through it is 100 µA, find ground. Assuming that the moving coil produces full-scale applied between the op amp's positive-input terminal and moving-coil meter. The voltmeter measures the voltage Vof very high input resistance that uses an inexpensive D2.46 Figure P2.46 shows a circuit for an analog voltmeter is +10 V. Does the meter resistance shown affect the voltmeter

#### FIGURE P2.46

the circuit in Fig. P2.47 is given by **D\*2.47** (a) Use superposition to show that the output of

$$\begin{split} v_O &= - \Big[ \frac{R_L}{R_{N1}} v_{N1} + \frac{R_L}{R_{N2}} v_{N2} + \dots + \frac{R_L}{R_{Nr}} v_{Nn} \Big] \\ &+ \Big[ 1 + \frac{R_L}{R_N} \Big[ \frac{R_P}{R_{P1}} v_{P1} + \frac{R_P}{R_{P2}} v_{P2} + \dots + \frac{R_P}{R_{Pn}} v_{Pn} \Big] \\ &\text{where } P - P \quad HP \quad H \dots HP \quad \text{and} \end{split}$$

where  $R_N = R_{N1}//R_{N2}//\cdots //R_{Nn}$  and  $R_P = R_{P1} / / R_{P2} / / \cdots / / R_{Pn} / / R_{P0}$

(b) Design a circuit to obtain

$$v_O = - \, 2 \, v_{N1} + v_{P1} + 2 \, v_{P2}$$

The smallest resistor used should be 10 kΩ.

#### FIGURE P2.47

- put is  $v_0 = v_{I1} + 3v_{I2} 2(v_{I3} + 3v_{I4})$ . (*Hint*: Use a structure similar to that shown in general form in Fig. P2.47.) D2.48 Design a circuit, using one ideal op amp, whose out-

- the circuit in Fig. P2.49. **2.49** Derive an expression for the voltage gain,  $v_O/v_l$ , of

#### FIGURE P2.49

- op amp. For  $v_0$  in terms of the input voltages  $v_1$  and  $v_2$ . Assume an ideal **2.50** For the circuit in Fig. P2.50, use superposition to find

- $v_2 = 10\sin(2\pi \times 60t) + 0.1\sin(2\pi \times 1000t)$ , volts  $v_1 = 10\sin(2\pi \times 60t) - 0.1\sin(2\pi \times 1000t)$ , volts

find  $v_o$ .