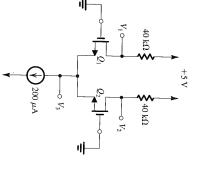

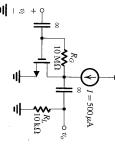

the following cases:  $V_t = 1$  V, and the process transconductance parameter  $k_n' = 100 \ \mu \text{A/V}^2$ . Assuming  $\lambda = 0$ , find  $V_1$ ,  $V_2$ , and  $V_3$  for each of **4.48** In the circuit of Fig. P4.48, transistors  $Q_1$  and  $Q_2$  have

(a)

$$(W/L)_1 = (W/L)_2 = 20$$

(b)  $(W/L)_1 = 1.5(W/L)_2 = 20$

(b)

$$(W/L)_1 = 1.5(W/L)_2 = 20$$

FIGURE P4.48

## SECTION 4.4: THE MOSFET AS AN AMPLIFIER

$V_{DD} = 5 \text{ V}, R_D = 24 \text{ k}\Omega, k'_n(W/L) = 1 \text{ mA/V}^2, \text{ and } V_t = 1 \text{ V}.$ **4.49** Consider the CS amplifier of Fig. 4.26(a) for the case

points A and B on the sketch of Fig. 4.26(c). (a) Find the coordinates of the two end points of the saturationregion segment of the amplifier transfer characteristic, that is,

on the transfer characteristic. Also, find the value of  $I_D$  and of the incremental gain  $A_v$  at the bias point. voltage  $V_{OV}$  of 0.5 V, find the coordinates of the bias point Q<sub>1</sub> (b) If the amplifier is biased to operate with an overdrive

from the incremental gain value calculated above? Why is results? What gain value does the combination of these ampli-What is the amplitude of the output voltage signal that there a difference? tudes imply? By what percentage is this gain value different applied at the input while the transistor remains in saturation? the largest amplitude of a sine-wave voltage signal that can be caused by the MOSFET's square-law characteristic, what is (c) For the situation in (b), and disregarding the distortion

region segment of the transfer characteristic. Prepare a table ditions, that is, for bias at various points along the saturationamplifier circuit studied in Example 4.8 for various bias con-\*4.50 We wish to investigate the operation of the CS

> (V), and the magnitude of the largest allowable negative-out- $V_{DS} = 1 \text{ V}, 2 \text{ V}, 3 \text{ V}, \dots, 10 \text{ V}$ ). Note that  $v_o^{\dagger}$  is determined by put signal  $v_o^-(V)$  for values of  $V_{DS} = V_{OQ}$  in the range of 1 V to the magnitude of the largest allowable positive-output signal  $v_{\sigma}^{+}$ giving the values of  $I_D$  (mA),  $V_{OV}(V)$ ,  $V_{GS} = V_{IQ}(V)$ ,  $A_v(V/V)$ ing the triode region. the MOSFET entering cutoff and  $v_o^-$  by the MOSFET enter-10 V, in increments of 1 V (i.e., there should be table rows for

the MOSFET's W/L? process transconductance parameter  $k'_n$  is 50  $\mu$ A/V<sup>2</sup>, what is be -10 V/V. What is the value of  $V_t$  for this transistor? If the ac measurements with small signals show the voltage gain to be 2 V and the gate-to-source bias voltage to be 1.2 V. Then, surements show the voltage across the drain resistor,  $V_{RD}$ , to 4.51 Various measurements are made on an NMOS amplifier for which the drain resistor  $R_D$  is 20 k $\Omega$ . First, dc mea-

here, let this lower limit be 0.2 V. Also, assume that  $V_{DD} = 5$  V. limit on the value of the overdrive voltage  $V_{OV}$ . For our purposes gain in Eq. (4.41). Various design considerations place a lower \*D4.52 Refer to the expression for the incremental voltage

to obtain maximum gain? What gain value is achievable? ±0.5 V, what dc bias voltage should be established at the drain What input signal results in a ±0.5-V output swing? (b) If we are required to allow for an output voltage swing of what is the maximum voltage gain achievable? (a) Without allowing any room for output voltage swing

lish a dc drain current of 100  $\mu$ A. For the given process technology,  $k_n'=100~\mu$ A/V². (c) For the situation in (b), find W/L of the transistor to estab-

(d) Find the required value of R<sub>D</sub>.

given in Eq. (4.41) can be written in as **4.53** The expression for the incremental voltage gain  $A_v$

$$A_v = -\frac{2(V_{DD} - V_{DS})}{V_{OV}}$$

transistor remains saturated is negative output signal peak  $\hat{v}_{c}$  that is achievable while the operation around the bias point, show that the largest possible output signal swing in the negative direction. Assuming linear where  $V_{DS}$  is the bias voltage at the drain (called  $V_{OQ}$  in the transistor at a lower  $V_{DS}$ . This, however, reduces the allowable and  $V_{OV}$ , the gain magnitude can be increased by biasing the text). This expression indicates that for given values of  $V_{DD}$

$$\hat{v_o} = (V_{DS} - V_{OV}) / \left(1 + \frac{1}{A_v}\right)$$

for which  $V_{DS} = 1 \text{ V}$ .  $A_v$ ,  $\hat{v}_o$ , and the corresponding  $\hat{v}_l$  for  $V_{DS} = 1$  V, 1.5 V, 2 V, and 2.5 V. If  $k_n'W/L = 1$  mA/V<sup>2</sup>, find  $I_D$  and  $R_D$  for the design For  $V_{DD} = 5$  V and  $V_{OV} = 0.5$  V, provide a table of values for

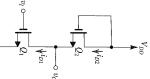

> range of  $v_l$  over which  $Q_1$  is operating in saturation, that is, for conduct equal drain currents. Using  $i_{D1} = i_{D2}$ , show that for the  $Q_2$  is zero, it will be operating in saturation at all times, even connected as a two-terminal device. Note that because  $v_{DG}$  of when  $v_l = 0$  and  $i_{D2} = i_{D1} = 0$ . Note also that the two transistors resistor  $R_D$  has been replaced with another NMOS transistor  $Q_2$ 4.54 Figure P4.54 shows a CS amplifier in which the load

$$V_{t1} \leq v_t \leq v_O + V_{t1}$$

the output voltage will be given by

$$v_{O} = V_{DD} - V_{\iota} + \sqrt{\frac{(W/L)_{1}}{(W/L)_{2}}} V_{\iota} - \sqrt{\frac{(W/L)_{1}}{(W/L)_{2}}} v_{I}$$

tions as a linear amplifier, even for large input signals. For where we have assumed  $V_{t1} = V_{t2} = V_r$ . Thus the circuit func- $\mu$ m), find the voltage gain.  $(W/L)_1 = (50 \ \mu\text{m}/0.5 \ \mu\text{m}) \text{ and } (W/L)_2 = (5 \ \mu\text{m}/0.5)$

FIGURE P4.54

## CIRCUITS SECTION 4.5: BIASING IN MOS AMPLIFIER

design, how far is the drain voltage from the edge of saturation? the drain current is 2 mA, with about one-third of the supply have chosen? Specify them to two significant digits. For your  $R_{G1}$  and  $R_{G2}$ . What are the values of  $R_{G1}$ ,  $R_{G2}$ ,  $R_{S}$ , and  $R_{D}$  that you voltage across each of  $R_S$  and  $R_D$ . Use 22 M $\Omega$  for the larger of  $\lambda = 0$ ,  $k'_n = 80 \mu \text{A/V}^2$ ,  $W = 240 \mu \text{m}$ , and  $L = 6 \mu \text{m}$ . Arrange that Fig. 4.30(c), using a 15-V supply. For the MOSFET,  $V_i = 1.2 \text{ V}$ , D4.55 Consider the classical biasing scheme shown in

significant digits. midway between cutoff and the beginning of triode operation. arrange to bias the NMOS transistor at  $I_D = 2$  mA with  $V_D$ **D4.56** Using the circuit topology displayed in Fig. 4.30(e), Use a gate-bias resistor of 10 M $\Omega$ . Specify  $R_S$  and  $R_D$  to two  $V_r = 0.8 \text{ V}, \lambda = 0, k_n' = 50 \mu \text{A/V}^2, W = 200 \mu \text{m}, \text{ and } L = 4 \mu \text{m}.$ The available supplies are ±15 V. For the NMOS transistor,

> \*D4.57 In an electronic instrument using the biasing values of current now result? standard 5% resistor value (refer to Appendix G). What extreme result? What value of R<sub>S</sub> should have been installed to limit from 1.3 to 2.4 V, what are the extreme values of  $I_D$  that may the maximum value of  $I_D$  to 0.15 mA? Choose an appropriate allow  $k'_n(W/L)$  to vary from 220 to 380  $\mu$ A/V<sup>2</sup> and  $V_r$  to vary What is the value of  $V_G$  created? If supplier specifications  $R_S$  to zero. Let  $V_{DD} = 12 \text{ V}$ ,  $R_{G1} = 5.6 \text{ M}\Omega$ , and  $R_{G2} = 2.2 \text{ M}\Omega$ . scheme shown in Fig. 4.30(c), a manufacturing error reduces

higher is used, what is the resulting percentage increase in  $I_D$ ? current results? If a transistor for which  $k'_n(WL)$  is 50% transistor has  $V_t = 2 \text{ V}$  and  $k'_n(W/L) = 2 \text{ mA/V}^2$ . What bias bias circuit of Fig. 4.30(c), with  $V_G = 4 \text{ V}$  and  $R_S = 1 \text{ k}\Omega$ . The 4.58 An enhancement NMOS transistor is connected in the

bias current results? for which  $V_t$  is 0.5 V less is used, what does  $V_S$  become? What found to be 2 V. What must  $V_i$  be for this device? If a device 4.59 The bias circuit of Fig. 4.30(c) is used in a design with  $k'_n(W/L) = 2 \text{ mA/V}^2$ , the source voltage was measured and  $V_G = 5 \text{ V}$  and  $R_S = 1 \text{ k}\Omega$ . For an enhancement MOSFET with

minal of the FET is zero. at the drain. Assume that the signal voltage on the source terthe largest possible voltage gain (and thus the largest possible ment MOSFET having  $V_t = 2 \text{ V}$  and  $k'_n(W/L) = 2 \text{ mA/V}^2$ . Let **D4.60** Design the circuit of Fig. 4.30(e) for an enhance- $R_D$ ) consistent with allowing a 2-V peak-to-peak voltage swing  $V_{DD} = V_{SS} = 10 \text{ V}$ . Design for a dc bias current of 1 mA and for

following two devices (use a 10-µA current in the voltage operates in saturation with  $V_D$  biased 1 V from the edge of the triode region, with  $I_D = 1$  mA and  $V_D = 3$  V, for each of the **D4.61** Design the circuit in Fig. P4.61 so that the transistor

(a)

$$|V_t| = 1 \text{ V}$$

and  $k_p W/L = 0.5 \text{ mA/V}^2$

(a)

$$|V_t| = 1$$

V and  $\kappa_p W/L = 0.5$  mA/V<sup>2</sup>

(b)  $|V_t| = 2$  V and  $k_p' W/L = 1.25$  mA/V<sup>2</sup>

For each case, specify the values of  $V_G$ ,  $V_D$ ,  $V_S$ ,  $R_1$ ,  $R_2$ ,  $R_S$ , and  $R_D$ .

FIGURE P4.61

to a particular transistor parameter whose variability might be  $K \equiv \frac{1}{2}K'(W/L)$  is defined as large. The sensitivity of  $I_D$  relative to the MOSFET parameter the bias current  $I_D$  is to evaluate the sensitivity of  $I_D$  relative \*\***D4.62** A very useful way to characterize the stability of

$$S_K^{I_D} \equiv \frac{\delta I_D/I_D}{\delta K/K} = \frac{\delta I_D}{\delta K} \frac{K}{I_D}$$

the sensitivity function in the design of the bias circuit of The purpose of this problem is to investigate the use of of K, provides the corresponding expected variability of  $I_D$ . Fig. 4.30(e). and its value, when multiplied by the variability (or tolerance)

(a) Show that for V<sub>t</sub> constant,

$$S_K^{I_D} = 1/(1 + 2\sqrt{KI_D}R_S)$$

- the required value of  $V_{ss}$ . in  $I_D$  = 100  $\mu\mathrm{A}$  with a variability of  $\pm1\%.$  Also, find  $V_{GS}$  and of  $\pm 10\%$  and  $V_t = 1$  V, find the value of  $R_S$  that would result (b) For a MOSFET having  $K = 100 \mu \text{A/V}^2$  with a variability

- expected variability of  $I_D$  in this case.  $I_D = 100 \mu A$ . Evaluate the sensitivity function, and give the (c) If the available supply  $V_{SS} = 5$  V, find the value of  $R_S$  for

- $V_D$ , and  $V_{DS}$  that result. the following two cases. In each case, find the voltages  $V_S$ ,  $R_D = 5 \text{ k}\Omega$ , and  $V_{DD} = 10 \text{ V}$ , consider the behavior in each of **4.63** For the circuit in Fig. 4.33(a) with I = 1 mA,  $R_G = 0$ ,

- (a)  $V_t = 1 \text{ V} \text{ and } k_n'W/L = 0.5 \text{ mA/V}^2$

- (b)  $V_t = 2 \text{ V}$  and  $k'_n W/L = 1.25 \text{ mA/V}^2$

- the voltages  $V_D$  and  $V_G$ . and  $V_{DD} = 10$  V. For each of the following two transistors, find **4.64** In the circuit of Fig. 4.32, let  $R_G = 10 \text{ M}\Omega$ ,  $R_D = 10 \text{ k}\Omega$ ,

- (a)  $V_t = 1 \text{ V}$  and  $k'_n W/L = 0.5 \text{ mA/V}^2$

- (b)  $V_t = 2 \text{ V}$  and  $k'_n W/L = 1.25 \text{ mA/V}^2$

- you choose? What values of current and  $V_D$  result? on the 5% resistor scale (see Appendix G), what value would drain current of 0.2 mA. If resistor values are limited to those  $V_t = 1 \text{ V}$  and  $k'_n(W/L) = 0.4 \text{ mA/V}^2$ , find  $R_D$  to establish a Fig. 4.32 with a 9-V supply and an NMOS device for which **D4.65** Using the feedback bias arrangement shown in

a design which biases the transistor at  $I_D = 2$  mA, with  $V_{DS}$ have you chosen? Specify all resistors to two significant digits. the feedback-bias network. What values of  $R_D$ ,  $R_{G1}$ , and  $R_{G2}$ signal swing at the drain. Use 22 M $\Omega$  as the largest resistor in large enough to allow saturation operation for a 2-V negative tor for which  $V_r = 1.2 \text{ V}$ ,  $k'_n W/L = 3.2 \text{ mA/V}^2$  and  $\lambda = 0$ , provide circuit of Fig. 4.32. Using a 6-V supply with an NMOS transis-**D4.66** Figure P4.66 shows a variation of the feedback-bias

## FIGURE P4.66

## AND MODELS SECTION 4.6: SMALL-SIGNAL OPERATION

second-harmonic distortion) is at frequency a, expressed as a percentage (known as the that the ratio of the signal at frequency  $-2\omega$  to that with amplitude  $V_{ge}$  and substitute  $v_{ge} = V_{ge} \sin \omega t$  in Eq. (4.57). duced by a MOSFET amplifier. Let the signal  $v_{gs}$  be a sine wave \*4.67 This problem investigates the nonlinear distortion intro-Using the trigonometric identity  $\sin^2 \theta = \frac{1}{2} - \frac{1}{2} \cos 2\theta$ ,

Second-harmonic distortion =

$$\frac{1}{4} \frac{V_{gs}}{V_{OV}} \times 100$$

overdrive voltage at which the transistor should be operated so that the second-harmonic distortion is kept to less than 1% If in a particular application  $V_{gs}$  is 10 mV, find the minimum

- point. Compare with the value of  $g_m$  obtained using Eq. (4.62). Let the transistor be biased at  $V_{OV} = 1$  V. For operation in **4.68** Consider an NMOS transistor having  $k_n'W/L = 2 \text{ mA/V}^2$ signal. Use these results to estimate  $g_m$  of the FET at this bias and subtracting the dc bias current  $I_D$ . Repeat for a -0.1-Vcollector current by evaluating the total collector current  $i_D$ is superimposed on  $V_{GS}$ , find the corresponding increment in saturation, what dc bias current  $I_D$  results? If a +0.1-V signal

- 4.69 Consider the FET amplifier of Fig. 4.34 for the case  $V_t = 2 \text{ V}, \ k_n'(W/L) = 1 \text{ mA/V}^2, \ V_{GS} = 4 \text{ V}, \ V_{DD} = 10 \text{ V}, \text{ and}$

Cas

- (a) Find the dc quantities I<sub>D</sub> and V<sub>D</sub>.

- (b) Calculate the value of g<sub>m</sub> at the bias point.

- (c) Calculate the value of the voltage gain. (d) If the MOSFET has  $\lambda = 0.01 \text{ V}^{-1}$ , find  $r_o$  at the bias point and calculate the voltage gain.

- used as a drain resistor. If a gain of at least 5 V/V is needed, 0.50-V peak output signal across a 50-k $\Omega$  load that can be \*D4.70 An NMOS amplifier is to be designed to provide a

what  $g_m$  is required? Using a dc supply of 3 V, what values of  $I_D$  and  $V_{OV}$  would you choose? What WL ratio is required if  $\mu_k C_{ox} = 100~\mu\text{AV}^{-2}$ ? If  $V_t = 0.8~\text{V}$ , find  $V_{CS}$

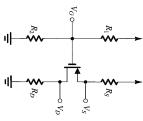

transistor with its T equivalent circuit of Fig. 4.39(d). Derive 4.74 For the NMOS amplifier in Fig. P4.74, replace the

expressions for the voltage gains  $v_s/v_i$  and  $v_d/v_i$ .

of the CS amplifier circuit of Fig. 4.34. First, use the voltage gain expression  $A_v = -g_m R_D$  together with Eq. (4.71) for  $g_m$ **\*D4.71** In this problem we investigate an optimum design

$$A_{v} = -\frac{2I_{D}R_{D}}{V_{OV}} = -\frac{2(V_{DD} - V_{D})}{V_{OV}}$$

ation is given by at the drain of  $|A_{v}|\hat{v}_{i}$  while maintaining saturation-mode operthat is consistent with allowing a negative signal voltage swing  $V_{OV} = m\hat{v}_i$ . Now, to maximize the voltage gain  $|A_{v}|$ , we the MOSFET to operate at an overdrive voltage  $V_{OV} \gg \hat{v}_i$ . Let Next, let the maximum positive input signal be  $\hat{v}_i$ . To keep the which is the expression we obtained in Section 4.4 (Eq. 4.41). design for the lowest possible  $V_D$ . Show that the minimum  $V_D$ second-harmonic distortion to an acceptable level, we bias

$$V_{D} = \frac{V_{OV} + \hat{v}_{i} + 2V_{DD}(\hat{v}_{i}/V_{OV})}{1 + 2(\hat{v}_{i}/V_{OV})}$$

this process technology  $k'_n = 100 \ \mu \text{A/V}^2$  $I_D = 100 \mu A$ , find the values of  $R_D$  and W/L, assuming that for 20 mV, and m = 10. If it is desired to operate this transistor at Now, find  $V_{OV}$ ,  $V_D$ ,  $A_v$ , and  $\hat{v}_o$  for the case  $V_{DD} = 3$  V,  $\hat{v}_i =$

- 4.72 In the table below, for enhancement MOS transistors and  $C_{ox} = 0.4 \text{ fF/}\mu\text{m}^2$ dimensions in  $\mu$ m. Assume  $\mu_n = 500 \text{ cm}^2 \text{N/s}$ ,  $\mu_p = 250 \text{ cm}^2 \text{N/s}$ . (4.70) or (4.71). In the table, current is in mA, voltage in V, and always possible to calculate  $g_m$  using one of Eqs. (4.69), entries as possible. Although some data is not available, it is operating under a variety of conditions, complete as many

- **4.73** An NMOS technology has  $\mu_r C_{ox} = 50 \,\mu\text{A/V}^2$  and  $V_t = 6.33 \,\text{m}$ results in  $g_m = 1$  mA/V at  $I_D = 0.5$  mA. Also, find the required  $V_{GS}$ . 0.7 V. For a transistor with  $L = 1 \mu \text{m}$ , find the value of W that

FIGURE P4.74

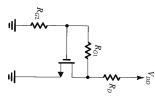

for I increased to 1 mA? is the voltage gain  $v_o/v_i$ ? What do  $V_D$  and the gain become  $|V_t| = 0.9 \text{ V}$  and  $V_A = 50 \text{ V}$  and operates with  $V_D = 2 \text{ V}$ . What \$.75 In the circuit of Fig. P4.75, the NMOS transistor has

FIGURE P4.75

|       |           |          |            | Se              |

|-------|-----------|----------|------------|-----------------|

| יטיטי | ר טי טי ט | 7222     | ZZZZ       | Туре            |

| 0.1   | 5.10 F    | - 0.0    | 10         | l <sub>p</sub>  |

|       | ω         | 1.8      | ω          | V <sub>65</sub> |

|       | 1         | 0.8      | 2<br>0.7   | [7]             |

| 5     | 4 4       | <b>.</b> | 0.5<br>0.5 | Vov             |

| 30    | 4000      | 10<br>40 | 50         | W               |

| ω     | 2         | 42,      | 1 1        | 7               |

|       |           | 25       |            | W/L             |

| ∞     | 500       |          |            | K'(W/L)         |

|       |           |          |            | 9,11            |