## EE 321 Analog Electronics, Fall 2011 Homework #7 solution

5.54. A common-emitter amplifier circuit operated with  $V_{CC} = +10$  V is biased at  $V_{CE} = +1$  V. Find the voltage gain, the maximum allowed output negative swing without the transistor entering saturation, and the corresponding maximum input signal permitted.

The voltage gain is

$$A = \frac{v_c}{v_{be}} = \frac{V_{CC} - V_{CE}}{V_T} = \frac{10 - 1}{25 \times 10^{-3}} = 360$$

The maximum negative output swing is

$$v_{c,\min} = V_{CESat} - V_C = 0.3 - 1 = -0.7 \,\mathrm{V}$$

The maximum input signal is

$$v_{be,\max} = -\frac{v_{c,\min}}{A} = \frac{0.7}{360} = 1.9 \,\mathrm{mV}$$

5.55. For the common-emitter amplifier circuit in Fig 5.26(a) with  $V_{CC} = +10$  V and  $R_C = 1 \text{ k}\Omega$ , find  $V_{CE}$  and the voltage gain at the following dc collector bias current: 1 mA, 2 mA, 5 mA, 8 mA, and 9 mA. For each, give maximum possible positive- and negative-output signal swing as determined by the need to keep the transistor in the active region. Present your result in a table.

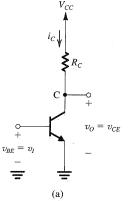

FIGURE 5.26 (a) Basic commo

The value of  $V_{CE}$  is

$$V_{CE} = V_{CC} - I_C R_C$$

This is tabulated in second column. The gain, A, is

$$A = -\frac{R_C I_C}{V_T}$$

This is tabulated in the third column. The minimum output voltage swing is determined by the edge of saturation,  $v_{CE,sat} = 0.3$  V. It is

$$v_{o,\min} = v_{CE,\text{sat}} - V_{CE}$$

This is tabulated in the fourth column. The maximum output voltage swing is determined by cutoff,  $i_C = 0$ , so that

$$v_{o,\max} = V_{CC} - V_{CE}$$

This is tabulated in the fifth column

| <br>$I_C$ (mA) | $V_{CE}$ (V) | A   | $v_{o,\min}$ (V) | $v_{o,\max}$ (V) |

|----------------|--------------|-----|------------------|------------------|

| 1              | 9            | 40  | -8.7             | 1                |

| 2              | 8            | 80  | -7.7             | 2                |

| 5              | 5            | 200 | -4.7             | 5                |

| 8              | 2            | 320 | -1.7             | 8                |

| 9              | 1            | 360 | -0.7             | 9                |

5.56. Consider the CE amplifier circuit of Fig 5.26(a) when operated with a dc supply  $V_{CC} = +5$  V. It is required to find the point at which the transistor should be biased; that is, find the value of  $V_{CE}$  so that the output sine-wave signal  $v_{ce}$  resulting from an input sine-wave signal  $v_{be}$  of 5 mV peak amplitude has the maximum possible magnitude. What is the peak amplitude of the output sine wave and the value of the gain obtained? Assume linear operation around the bias point. (Hint: To obtain the maximum possible output amplitude for a given input, you need to bias the transistor as close to the edge of saturation as possible without entering saturation at any time, that is without,  $v_{CE}$  decreasing below 0.3 V.

FIGURE 5.26 (a) Basic comme

The maximum negative output swing is  $-V_o = -g_m R_C V_i$ , which would make the bias point equal to

$$V_{CE} = V_{CE,\text{sat}} + V_o = V_{CE,\text{sat}} + g_m R_C V_i = V_{CE,\text{sat}} + \frac{I_C R_C}{V_T} V_i$$

Note also that

$$V_{CE} = V_{CC} - I_C R_C$$

Eliminating  $I_C R_C$  we get

$$V_{CE} = V_{CE,\text{sat}} + \frac{V_{CC} - V_{CE}}{V_T} V_i$$

$$V_{CE} \left(1 + \frac{V_i}{V_T}\right) = V_{CE,\text{sat}} + \frac{V_{CC}}{V_T} V_i$$

$$V_{CE} = \frac{V_{CE,\text{sat}} + \frac{V_{CC}}{V_T} V_i}{1 + \frac{V_i}{V_T}} = \frac{0.3 + \frac{5}{25} \times 5}{1 + \frac{5}{25}} = 1.13 \text{ V}$$

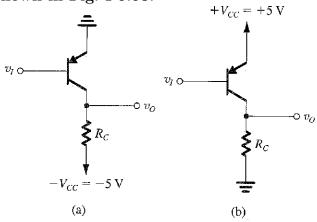

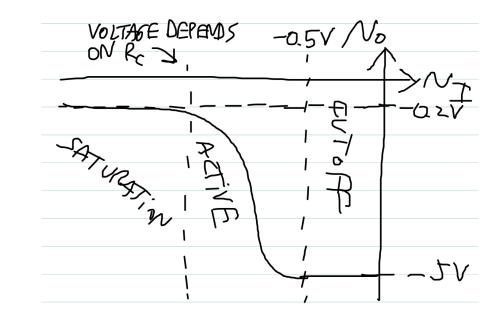

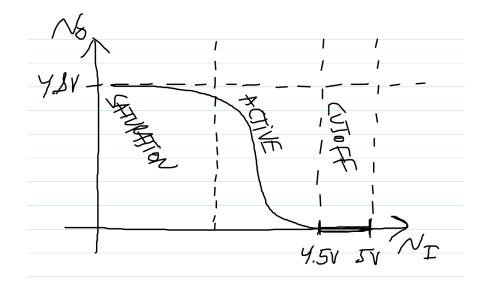

5.58. Sketch and label the voltage transfer characteristics of the pnp commonemitter amplifiers shown in Fig. P5.58.

(a)

(b)

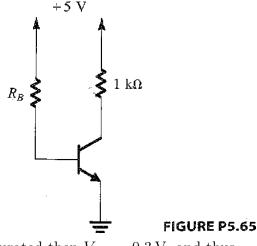

5.65. For the circuit in Fig. P5.56 select a value for  $R_B$  so that the transistor saturates with an overdrive factor of 10. The BJT is specified to have a minimum  $\beta$  of 20 and  $V_{CE \text{ sat}} = 0.2 \text{ V}$ . What is the value of forced  $\beta$  archieved?

When the transistor is saturated then  $V_{CE} = 0.3 \text{ V}$ , and thus

$$I_C = \frac{V_{CC} - V_{CE \text{ sat}}}{R_C} = \frac{5 - 0.2}{1} = 4.8 \text{ mA}$$

To get a overdrive factor of 10 means that  $\frac{beta}{\beta_{\text{forced}}} = 10$ . This result in  $\beta_{\text{forced}} = \frac{\beta}{10} = 2$ . The base current is then  $I_B = \frac{I_C}{\beta_{\text{forced}}} = \frac{4.8}{2} = 2.4 \text{ mA}$ , and the required value of the base resistor is

$$R_B = \frac{V_{CC} - V_{BE}}{I_B} = \frac{5 - 0.7}{2.4} = 1.8 \,\mathrm{k\Omega}$$