# EE 308: Microcontrollers AVR Architecture

Aly El-Osery

Electrical Engineering Department New Mexico Institute of Mining and Technology Socorro, New Mexico, USA

January 23, 2019

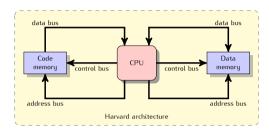

#### Harvard Architecture overview

- Separate buses for accessing code and data

- Faster

- Less delays

- Requires more hardware

## Data, address and control lines

- Data lines carry information in and out of the CPU. More lines results in faster data transfer but more complex and more expensive.

- Address lines identifies the devices and memory to be connected to the CPU

- Control lines control devices' signals for read/write as directed by the CPU

#### Data bus

- Carries data to and from RAM, ROM, and other devices

- More data lines facilitates more data being transferred at a time but results in more complex and expensive CPU

- Data buses are bidirectional

#### Address bus

- Number of address lines determines the number of locations that can be addressed

- Address buses are unidirectional

- For n lines there are  $2^n$  locations (e.g., memory) that can be addressed

- For example, 16 address lines can provide  $2^{16} = 65,536$  addressable memory, i.e., 64KB?

#### Address bus

5 / 23

- Number of address lines determines the number of locations that can be addressed

- Address buses are unidirectional

- For n lines there are  $2^n$  locations (e.g., memory) that can be addressed

- For example, 16 address lines can provide  $2^{16} = 65,536$  addressable memory, i.e., 64KB?

- 1KB = 1024 Bytes

#### Control bus

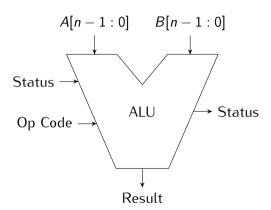

- Select operations of the Arithmetic Logic Unit (ALU)

- Selects read/write for the memory

# Types of memory

- Register file: embedded in the CPU for fast operations

- Code memory: ROM typically flash

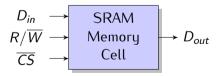

- Data memory: RAM typically SRAM

# Classification of memory

- Volatile

- Content is lost when power is switched off

- Known as RAM (Random Access Memory)

- Could be static (SRAM) or dynamic (DRAM)

- Non-Volatile

- Retains content even when no power is provided

- Known as ROM (Read Only Memory)

- Different types: ROM, PROM, EPROM, EEPROM, FLASH

- Made of flipflops

- Requires 6 transistors each

- Each cell holds only 1 bit

- Using address decoders, how many address lines are needed to address 16Kbits memory?

- Requires only one transistor per bit

- Information is stored in a capacitor

- Less silicon area is needed

- Can achieve more memory per a given area

- Needs refreshing due to leakage

- Slower than SRAM but cheaper

- Uses multiplexers/demultiplexers to cut the required address lines in half

#### Non-volatile memory

• Read Only Memory (ROM): Can't be overwritten, function determined by manufacturer, common type is Mask-ROM (MROM).

## Non-volatile memory

11 / 23

- Read Only Memory (ROM): Can't be overwritten, function determined by manufacturer, common type is Mask-ROM (MROM).

- Programmable ROM (PROM): Matrix is memory with intact fuse and default value of

Short high current pulse is applied to selected cells destroying the fuse and the logical value for those cells become 0.

## Non-volatile memoru

- Read Only Memory (ROM): Can't be overwritten, function determined by manufacturer, common type is Mask-ROM (MROM).

- Programmable ROM (PROM): Matrix is memory with intact fuse and default value of 1. Short high current pulse is applied to selected cells destroying the fuse and the logical value for those cells become 0.

- Erasable PROM (EPROM): Programmed by physical process called avalanche *injection.* Can be erased by exposing the chip to UV for about 30 min.

## Non-volatile memoru

- Read Only Memory (ROM): Can't be overwritten, function determined by manufacturer, common type is Mask-ROM (MROM).

- Programmable ROM (PROM): Matrix is memory with intact fuse and default value of 1. Short high current pulse is applied to selected cells destroying the fuse and the logical value for those cells become 0.

- Erasable PROM (EPROM): Programmed by physical process called avalanche *injection.* Can be erased by exposing the chip to UV for about 30 min.

- Electrically EPROM (EEPROM): Similar to EPROM but has charge pumps provided on the chip instead of UV. Good for about 100,000 cycles.

- Read Only Memory (ROM): Can't be overwritten, function determined by manufacturer, common type is Mask-ROM (MROM).

- Programmable ROM (PROM): Matrix is memory with intact fuse and default value of

Short high current pulse is applied to selected cells destroying the fuse and the logical value for those cells become 0.

- Erasable PROM (EPROM): Programmed by physical process called *avalanche injection*. Can be erased by exposing the chip to UV for about 30 min.

- Electrically EPROM (EEPROM): Similar to EPROM but has charge pumps provided on the chip instead of UV. Good for about 100,000 cycles.

- Flash: Similar to EEPROM but memory is erased in blocks. Used for storing code. It is cheaper but good for around 10,000 cycles.

# Memory mapping

- Separate memory addressing: need to address each memory, SRAM, FLASH, or EEPROM separately

- Single memory range: map different memory into a single memory range

# Little endian vs. big endian

Given a 16-bit value, for example 0xB60F, it is desired to save it into memory location 0x100 one byte at a time which byte gets written in the high byte and which one gets written in the low byte

• Little endian: used by most microcontrollers including AVR and Intel microprocessors

|       | High Byte | Low Byte |

|-------|-----------|----------|

| 0×100 | В6        | 0F       |

• Big endian: used by Freescale

|       | High Byte | Low Byte |  |

|-------|-----------|----------|--|

| 0x100 | 0F        | B6       |  |

## Addressing modes

Immediate (single-register): operand is a register and may have a constant value as a second operand, e.g.,

```

NEG R18 ;negate the content of R18 LDI R19,0x06 ;load 0x06 into R19

```

• Register: two registers hold the data to be manipulated

```

ADD R20, R23 ; add R23 to R20 and store the result in R20

```

• Direct: operand is a memory location

```

LDS R19,0x560 ;load R19 with the content of mem loc 0x560 STS 0x40,R19 ;store R19 to data space location 0x40

```

• Register indirect: operand is a register but it points to the memory location

```

LDI XL,0x30 ;load R26 (low byte of X) with 0x30

LDI XH,0x01 ;load R27 (high byte of X) with 0x01

LD R18,X ;load R18 with content of memory 0x130

```

Auto-increment/auto-decrement: content of register is pre- or post- incremented/decremented after/before memory access

```

LD Rn,X+ ; load Rn with content pointed to by X then inc X

LD Rn,-X ; decrement X then load Rn by contented pointed to by new X

```

# Arithmetic Logic Unit (ALU)

- Takes two inputs

- Performs arithmetic and logic operations

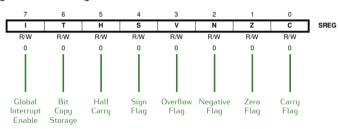

# Status register

## 8-bit register used by the ALU to indicate arithmetic conditions

Bit 0x3F (0x5F) Read/Write Initial Value

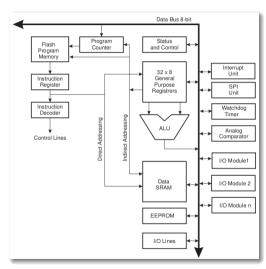

CPU architecture

- Control unit: controls devices, data path and determines which instruction to be executed

- Program counter: address of the next instruction to be executed

- Stack: memory used by the CPU to keep track of return addresses and register contents when branching, servicing an interrupt or executing a subroutine

- Stack pointer: points to the current position in the stack

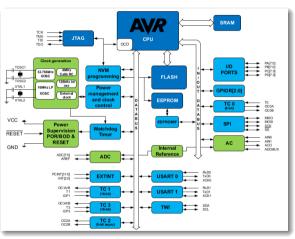

- RISC with Harvard architecture

- Code ROM

- Data RAM

- Data EEPROM

- Timers

- I/O ports

- ADC

- PWM

- Communication interfaces: USART, SPI, I2C (TWI), CAN, USB

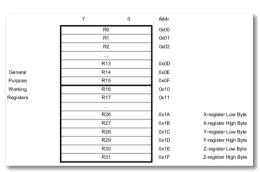

#### General purpose registers

- Register provide fast method for processing

- The registers are 8-bit wide

- Most operations can be executed in one cycle

|            | 15         | XH |     | XL        | 0 |

|------------|------------|----|-----|-----------|---|

| X-register | 7          |    | 0 7 |           | 0 |

|            | R27 (0x1B) |    | R:  | 26 (0x1A) |   |

|            |            |    |     |           |   |

|            | 15         | YH |     | YL        | 0 |

| Y-register | 7          |    | 0 7 |           | 0 |

|            | R29 (0x1D) |    | R   | 28 (0x1C) |   |

| Z-register | 15         | ZH |     | ZL        | 0 |

|            | 7          | 0  | 7   | 0         |   |

|            | R31 (0x1F) |    | R   | 30 (0x1E) |   |

# Some key specifics

- Instructions are either 2-bytes or 4-bytes

- Data lines to the data memory are 8-bit

- Data lines to the program memory are 16-bit

- Stack pointer is 16-bit

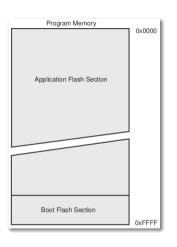

# Memory map

| Data Memory                |                 |

|----------------------------|-----------------|

| 32 Registers               | \$0000 - \$001F |

| 64 I/O Registers           | \$0020 - \$005F |

| 160 Ext I/O Reg.           | \$0060 - \$00FF |

| Internal SRAM<br>(16K x 8) | \$0100          |

|                            | \$40FF          |

- I/Os and peripherals are placed in I/O space

- I/O addresses are offset from memory address by 0x20

- $\bullet$  I/O registers in the range 0x00 to 0x1F are directly bit accessible

- IN and OUT commands must use addresses in the range 0x00 to 0x3F

- When using LD and ST commands I/O registers are addressed as data space and therefore 0x20 must be added to their addresses

## Atmega1284

- RISC architecture

- 131 instructions (most executes in single clock cycle)

- 128K bytes code ROM

- 4K bytes EEPROM

- 16K bytes SRAM

- JTAG

- Timers/counters, PWM, 8-channel 10bit ADC

- Watchdog timer

- USART, SPI, I2C