| Name |

|------|

|------|

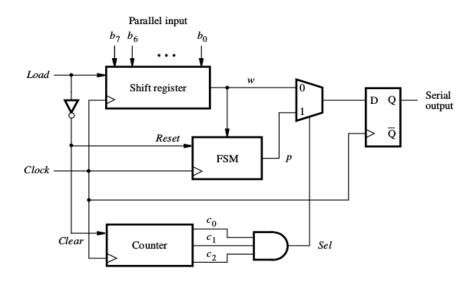

Assume that the Transmitter of the figure below accepts parallel data,  $\mathbf{B} = \mathbf{b}_7$ ,  $\mathbf{b}_6$ , ...,  $\mathbf{b}_0$ , representing ASCII characters. Assume also that bit  $\mathbf{b}_7$  is set to  $\mathbf{0}$ . The circuit is supposed to generate a parity bit,  $\mathbf{p}$ , and send it instead of  $\mathbf{b}_7$  as a part of the serial transfer. The Figure below gives a possible circuit. An **FSM** is used to generate the parity bit, which is included in the output stream by using a multiplexer. A three-bit counter is used to determine when the  $\mathbf{p}$  bit is transmitted, which happens when the count reaches  $\mathbf{7}$ .

## 1. - Design the desired FSM.

## 2.- Design a Receiver that detects errors in one of the bits of each byte received