- Addition and Subtraction of Hexadecimal Numbers

- Simple assembly language programming

- A simple Assembly Language Program

- o Assembling an Assembly Language Program

- Simple 9S12 programs

- Hex code generated from a simple 9S12 program

- Things you need to know for 9S12 assembly language programming

#### • Introduction to Addressing Modes

- o Most instructions operate on data in memory

- Addressing mode used to find address of data in memory

- MC9S12 Addressing modes: Inherent, Extended, Direct, Immediate, Indexed, and Relative Modes

# A Simple MC9S12 Program

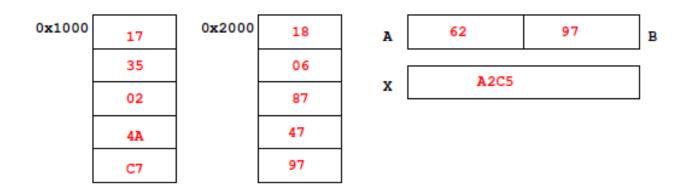

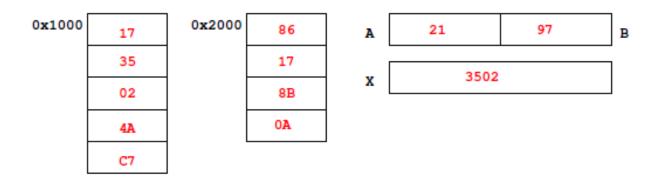

• All programs and data must be placed in memory between address **0x1000** and **0x3BFF**. For our programs we will put the first instruction at **0x2000**, and the first data byte at **0x1000**

• Consider the following program:

| ldaa \$1000 | ; Put contents of memory at 0x1000 into A |

|-------------|-------------------------------------------|

| inca        | ; Add one to A                            |

| staa \$1001 | ; Store the result into memory at 0x1001  |

| swi         | ; End program                             |

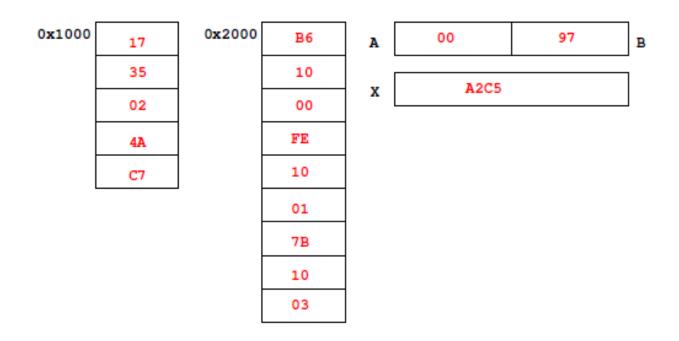

• If the first instruction is at address 0x2000, the following bytes in memory will tell the MC9S12 to execute the above program:

| <u>Address</u> | Value | <u>Instruction</u> |

|----------------|-------|--------------------|

| 0x2000         | B6    | ldaa \$1000        |

| 0x2001         | 10    |                    |

| 0x2002         | 00    |                    |

| 0x2003         | 42    | inca               |

| 0x2004         | 7A    | staa \$1001        |

| 0x2005         | 10    |                    |

| 0x2006         | 01    |                    |

| 0x2007         | 3F    | swi                |

• If the contents of address 0x1000 were 0xA2, the program would put an 0xA3 into address 0x1001.

#### A Simple Assembly Language Program.

• It is difficult for humans to remember the numbers (op codes) for computer instructions. It is also hard for us to keep track of the addresses of numerous data values. Instead we use words called mnemonics to represent instructions, and labels to represent addresses, and let a computer programmer called an assembler to convert our program to binary numbers (machine code).

• Here is an assembly language program to implement the previous program:

| prog equ \$2000<br>data equ \$1000             | ; Start program at 0x2000<br>; Data value at 0x1000 |

|------------------------------------------------|-----------------------------------------------------|

| org prog                                       |                                                     |

| ldaa input<br>inca                             |                                                     |

| staa result<br>swi                             |                                                     |

| org data<br>input: dc.b \$A2<br>result: ds.b 1 |                                                     |

• We would put this code into a file and give it a name, such as **main.s**. (Assembly language programs usually have the extension .s or .asm.)

• Note that equ, org, dc.b and ds.b are not instructions for the MC9S12 but are **directives** to the assembler which make it possible for us to write assembly language programs. There are called assembler directives or pseudo-ops. For example the pseudo-op **org** tells the assembler that the starting address (origin) of our program should be 0x2000.

#### Assembling an Assembly Language Program

• A computer program called an assembler can convert an assembly language program into machine code.

• The assembler we use in class is a commercial compiler from Freescale called CodeWarrior (Eclipse IDE).

• The assembler will produce a file called **main.lst**, which shows the machine code generated.

Freescale HC12-Assembler (c) Copyright Freescale 1987-2009

| Abs. | Rel. | Loc Obj. code  | Source line                        |

|------|------|----------------|------------------------------------|

|      |      |                |                                    |

| 1    | 1    |                |                                    |

| 2    | 2    | 0000 2000      | prog equ \$2000 ; Start program at |

| 0x20 | 00   |                |                                    |

| 3    | 3    | 0000 1000      | data equ \$1000 ; Data value at    |

| 0x10 | 00   |                |                                    |

| 4    | 4    |                |                                    |

| 5    | 5    |                | org prog                           |

| 6    | 6    |                |                                    |

| 7    | 7    | a002000 B610 0 | 0 Idaa input                       |

| 8    | 8    | a002003 42     | inca                               |

| 9    | 9    | a002004 7A10 0 | 1 staa result                      |

| 10   | 10   | a002007 3F     | swi                                |

| 11   | 11   |                |                                    |

| 12   | 12   |                | org data                           |

| 13   | 13   | a001000 A2     | input: dc.b \$A2                   |

| 14   | 14   | a001001        | result: ds.b 1                     |

This will produce a file called Project.abs.s19 which we load into the MC9S12.

S06B0000433A5C446F63756D656E747320616E642053657474696E67 73 S1051000A20048 S10B2000B61000427A10013F02 S9030000FC

- The first line of the S19 file starts with a S0: the **S0** indicates that it **is the first line**.

- The first line form CodeWarrior is too long for the DBug-12 monitor. You will need to delete it before loading the file into the MC9S12.

- The last line of the S19 file starts with a S9: the **S9** indicates that it **is the last line**.

- The other lines begin with a S1: the **S1** indicates these lines **are data** to be loaded into the MC9S12 memory.

- Here is the second line (with some spaces added):

S1 0B 2000 B6 1000 42 7A 1001 3F 02

- On the second line, the S1 if followed by a **0B**. This tells the loader that there this line has 11 (0x0B) bytes of data follow.

- The count 0B is followed by **2000**. This tells the loader that the data (program) should be put into memory starting with address 0x2000.

- The next 16 hex numbers B61000427A10013F are the 8 bytes to be loaded into memory. You should be able to find these bytes in the **main.lst** file.

• The last two hex numbers, **0x02**, is a one byte checksum, which the loader can use to make sure the data was loaded correctly.

| (c) C | opyrig | IC12-Assembler<br>ht Freescale 198<br>Loc Obj. code |       | ce line                           |

|-------|--------|-----------------------------------------------------|-------|-----------------------------------|

| <br>1 | <br>1  |                                                     |       |                                   |

| 2     | 2      | 0000 2000                                           | prog  | equ \$2000 ; Start program at     |

| 0x20  | 00     |                                                     |       |                                   |

| 3     | 3      | 0000 1000                                           | data  | equ \$1000 ; Data value at 0x1000 |

| 4     | 4      |                                                     |       |                                   |

| 5     | 5      |                                                     | org   | prog                              |

| 6     | 6      |                                                     |       |                                   |

| 7     | 7      | a002000 B610 (                                      | )0    | ldaa input                        |

| 8     | 8      | a002003 42                                          |       | inca                              |

| 9     | 9      | a002004 7A10 (                                      | )1    | staa result                       |

| 10    | 10     | a002007 3F                                          |       | swi                               |

| 11    | 11     |                                                     |       |                                   |

| 12    | 12     |                                                     | org   | data                              |

| 13    | 13     | a001000 A2                                          | -     | input: dc.b \$A2                  |

| 14    | 14     | a001001                                             | resul | t: ds.b 1                         |

What will program do?

| • ldaa input  | : Load contents of 0x1000 into A<br>(0xA2 into A)                   |

|---------------|---------------------------------------------------------------------|

| • inca        | : Increment A<br>( $0xA2 + 1 = 0xA3 \rightarrow A$ )                |

| • staa result | : Store contents of A to address 0x1001<br>(0xA3 -> address 0x1001) |

| • swi         | : Software interrupt (Return control to DBug-12<br>Monitor)         |

### **Simple Programs for the MC9S12**

A simple MC9S12 program fragment

org \$2000 ldaa \$1000 asra staa \$1001

<u>A simple MC9S12 program with assembler directives</u>

prog: equ \$2000 equ \$1000 org prog ldaa input asra staa result swi org data dc.b \$07 result: ds.b 1

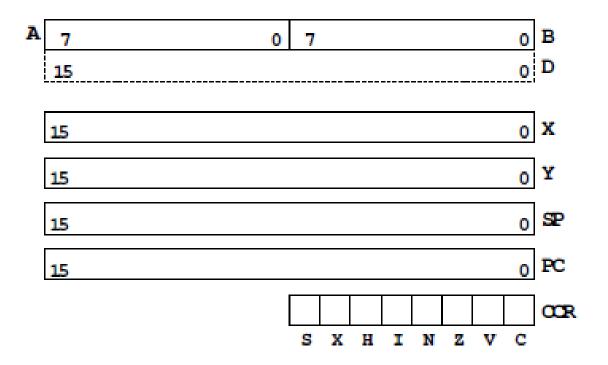

<u>MC9S12 Programming Model</u> — The registers inside the MC9S12 <u>CPU the programmer needs to know about</u>

<u>Things you need to know to write MC9S12 assembly language</u> <u>programs</u>

HC12 Assembly Language Programming

#### **Programming Model**

**MC9S12 Instructions**

**Addressing Modes**

**Assembler Directives**

## **Addressing Modes for the MC9S12**

• Almost all MC9S12 instructions operate on memory

• The address of the data an instruction operates on is called the <u>effective address</u> of that instruction.

• Each instruction has information which tells the MC9S12 the address of the data in memory it operates on.

• The <u>addressing mode</u> of the instruction tells the MC9S12 how to figure out the effective address for the instruction.

• Each MC9S12 instructions consists of <u>a one or two byte op code</u> which tells the HCS12 what to do and what addressing mode to use, followed, when necessary by one or more bytes which tell the HCS12 how to determine the effective address.

– All two-byte op codes begin with an \$18.

• For example, the LDAA instruction has 4 different op codes (86, 96, B6, A6), one for each of the 4 different addressing modes (IMM, DIR, EXT, IDX).

Core User Guide - \$12CPU15UG V1.2

Load A

$\begin{array}{ll} \text{Operation} & (M) \Rightarrow A \\ & \text{or} \end{array}$

$\operatorname{imm} \Rightarrow A$

Loads A with either the value in M or an immediate value.

#### CCR Effects

| s | Х | Н | Т | Ν | Ζ | ۷ | С |

|---|---|---|---|---|---|---|---|

| - | - | - | 1 | Δ | Δ | 0 | - |

N: Set if MSB of result is set; cleared otherwise

Z: Set if result is \$00; cleared otherwise

V: Cleared

#### Code and

CPU

Cycles

| Source Form                                                                                                                                        | Address<br>Mode                | Machine<br>Code (Hex)                                                            | CPU Cycles                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------|

| LDAA #opr8i<br>LDAA opr8a<br>LDAA opr16a<br>LDAA oprx0_xysppc<br>LDAA oprx9,xysppc<br>LDAA oprx16,xysppc<br>LDAA [D,xysppc]<br>LDAA [oprx16,xysppc | IDX<br>IDX1<br>IDX2<br>[D,IDX] | 86 ii<br>96 dd<br>B6 hh 11<br>A6 xb<br>A6 xb ff<br>A6 xb ee ff<br>A6 xb<br>A6 xb | P<br>rPf<br>rPO<br>rPf<br>rPO<br>frPP<br>flfrPf<br>flPrPf |

### The MC9S12 has 6 addressing modes

Most of the HC12's instructions access data in memory There are several ways for the HC12 to determine which address to access

**Effective address:** Memory address used by instruction

**Addressing mode:** How the MC9S12 calculates the effective address

# **MC9S12 ADDRESSING MODES:**

**INH** Inherent

IMM Immediate

**DIR** Direct

EXT Extended

REL Relative (used only with branch instructions)

IDX Indexed (won't study indirect indexed mode)

# The Inherent (INH) addressing mode

Instructions which work only with registers inside ALU

| ABA<br>18 06            | ; Add B to A (A) + (B) $\rightarrow$ A |

|-------------------------|----------------------------------------|

| CLRA<br><mark>87</mark> | ; Clear A 0 $\rightarrow$ A            |

| ASRA<br>47              | ; Arithmetic Shift Right A             |

| TSTA<br>97              | ; Test A (A) – 0x00 Set CCR            |

#### The MC9S12 does not access memory

# There is no effective address

### The Extended (EXT) addressing mode

Instructions which give the 16–bit address to be accessed

| LDAA \$1000     | ; (\$1000) $\rightarrow$ A              |

|-----------------|-----------------------------------------|

| <b>B6 10 00</b> | Effective Address: \$1000               |

| LDX \$1001      | ; ( $$1001$ : $$1002$ ) $\rightarrow$ X |

| FE 10 01        | Effective Address: $$1001$              |

| STAB \$1003     | ; (B) $\rightarrow$ \$1003              |

| <b>7B 10 03</b> | Effective Address: \$1003               |

# Effective address is specified by the two bytes following op code

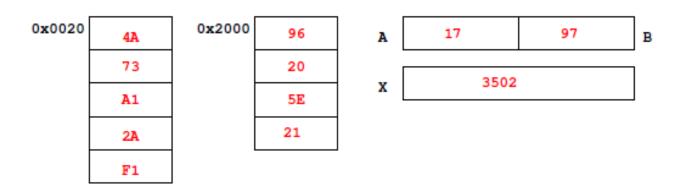

# The Direct (DIR) addressing mode

Direct (DIR) Addressing Mode

Instructions which give 8 LSB of address (8 MSB all 0)

| LDAA \$20    | ; (\$0020) $\rightarrow$ A        |

|--------------|-----------------------------------|

| <b>96 20</b> | Effective Address: \$0020         |

| STX \$21     | ; (X) $\rightarrow$ \$0021:\$0022 |

| <b>5E 21</b> | Effective Address: \$0021         |

8 LSB of effective address is specified by byte following op code

### The Immediate (IMM) addressing mode

Value to be used is part of instruction

| LDAA #\$17   | ; $17 \rightarrow A$      |

|--------------|---------------------------|

| <b>B6 17</b> | Effective Address: PC + 1 |

|              |                           |

| ADDA #10     | ; (A) + $A \rightarrow A$ |

| 8B 0A        | Effective Address: PC + 1 |

# Effective address is the address following the op code

# The Indexed (IDX, IDX1, IDX2) addressing mode

Effective address is obtained from X or Y register (or SP or PC)

Simple Forms

| LDAA 0,X<br><b>A6 00</b> | ; Use (X) as address to get value to put in A<br>Effective address: contents of X       |  |  |

|--------------------------|-----------------------------------------------------------------------------------------|--|--|

| ADDA 5,Y<br><b>AB 45</b> | ; Use (Y) + 5 as address to get value to add to<br>Effective address: contents of Y + 5 |  |  |

| More Complic             | cated Forms                                                                             |  |  |

| INC 2,X-                 | ; Post-decrement Indexed<br>; Increment the number at address (X),                      |  |  |

| 62 3E                    | ; then subtract 2 from X<br>Effective address: contents of X                            |  |  |

| INC 4,+X                 | ; Pre–increment Indexed<br>; Add 4 to X<br>; then increment the number at address (X)   |  |  |

| 62 23                    | Effective address: contents of $X + 4$                                                  |  |  |

#### **Different types of indexed addressing modes** (Note: We will not discuss indirect indexed mode)

# **INDEXED ADDRESSING MODES**

|                 | Banple                           | Effective<br>Address          | Offset                          | Value in X<br>After Done | Regi <i>s</i> ters<br>To Use |

|-----------------|----------------------------------|-------------------------------|---------------------------------|--------------------------|------------------------------|

| Constant Offset | LDAA n,X                         | (X)+n                         | 0 to FFFF                       | (X)                      | X, Y, SP, PC                 |

| Constant Offset | LDAA - n, X                      | (X)-n                         | 0 to FFFF                       | (X)                      | X, Y, SP, PC                 |

| Postincrement   | LDAA n, X+                       | (X)                           | 1 to 8                          | (X)+n                    | X, Y, SP                     |

| Preincrement    | LDAA n,+X                        | (X)+n                         | 1 to 8                          | (X)+n                    | X, Y, SP                     |

| Postdecrement   | LDAA n, X-                       | (X)                           | 1 to 8                          | (X)-n                    | X, Y, SP                     |

| Predecrement    | LDAA n,-X                        | (X)-n                         | 1 to 8                          | (X)-n                    | X, Y, SP                     |

| ACC Offset      | IDAA A,X<br>IDAA B,X<br>IDAA D,X | (X)+(A)<br>(X)+(B)<br>(X)+(D) | 0 to FF<br>0 to FF<br>0 to FFFF | (X)                      | X, Y, SP, PC                 |

(Does not include indirect modes)

#### The data books list three different types of indexed modes:

- Table 4.2 of the Core Users Guide shows details

- **IDX:** One byte used to specify address

- Called the postbyte

- Tells which register to use

- Tells whether to use autoincrement or autodecrement

- Tells offset to use

- **IDX1:** Two bytes used to specify address

- First byte called the postbyte

- Second byte called the extension

- Postbyte tells which register to use, and sign of offset

- Extension tells size of offset

- **IDX2:** Three bytes used to specify address

- First byte called the postbyte

- Next two bytes called the extension

- Postbyte tells which register to use

- Extension tells size of offset

| Addressing Mode                            | Source Format                                | Abbreviation | Description                                                                                                             |

|--------------------------------------------|----------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| Inherent                                   | INST<br>(no externally<br>supplied operands) | INH          | Operands (if any) are in CPU registers                                                                                  |

| Immediate                                  | INST #opr8i<br>or<br>INST #opr16i            | IMM          | Operand is included in instruction stream<br>8- or 16-bit size implied by context                                       |

| Direct                                     | INST opr8a                                   | DIR          | Operand is the lower 8 bits of an address<br>in the range \$0000-\$00FF                                                 |

| Extended                                   | INST opr16a                                  | EXT          | Operand is a 16-bit address                                                                                             |

| Relative                                   | INST rel8<br>or<br>INST rel16                | REL          | An 8-bit or 16-bit relative offset from the current pc<br>is supplied in the instruction                                |

| Indexed<br>(5-bit offset)                  | INST oprx5,xysp                              | IDX          | 5-bit signed constant offset<br>from X, Y, SP, or PC                                                                    |

| Indexed<br>(pre-decrement)                 | INST oprx3,-xys                              | IDX          | Auto pre-decrement x, y, or sp by 1 ~ 8                                                                                 |

| Indexed<br>(pre-increment)                 | INST oprx3,+xys                              | IDX          | Auto pre-increment x, y, or sp by 1 ~ 8                                                                                 |

| Indexed<br>(post-decrement)                | INST oprx3,xys-                              | IDX          | Auto post-decrement x, y, or sp by 1 ~ 8                                                                                |

| Indexed<br>(post-increment)                | INST oprx3,xys+                              | IDX          | Auto post-increment x, y, or sp by 1 ~ 8                                                                                |

| Indexed<br>(accumulator offset)            | INST abd,xysp                                | IDX          | Indexed with 8-bit (A or B) or 16-bit (D)<br>accumulator offset from X, Y, SP, or PC                                    |

| Indexed<br>(9-bit offset)                  | INST oprx9,xysp                              | IDX1         | 9-bit signed constant offset from X, Y, SP, or PC<br>(lower 8 bits of offset in one extension byte)                     |

| Indexed<br>(16-bit offset)                 | INST oprx16,xysp                             | IDX2         | 16-bit constant offset from X, Y, SP, or PC<br>(16-bit offset in two extension bytes)                                   |

| Indexed-Indirect<br>(16-bit offset)        | INST [oprx16,xysp]                           | [IDX2]       | Pointer to operand is found at<br>16-bit constant offset from X, Y, SP, or PC<br>(16-bit offset in two extension bytes) |

| Indexed-Indirect<br>(D accumulator offset) | INST [D,xysp]                                | [D,IDX]      | Pointer to operand is found at<br>X, Y, SP, or PC plus the value in D                                                   |

#### Table 3-1. M68HC12 Addressing Mode Summary

# **Relative (REL) Addressing Mode**

The relative addressing mode is used only in <u>branch</u> and <u>long</u> <u>branch</u> instructions.

Branch instruction: One byte following op code specifies how far to branch

<u>Treat the offset as a signed number</u>; add the offset to the address following the current instruction to get the address of the instruction to branch to

- **(BRA)** 20 35 PC + 2 + 0035  $\rightarrow$  PC

- (BRA) 20 C7 PC + 2 + FFC7  $\rightarrow$  PC PC + 2 - 0039  $\rightarrow$  PC

Long branch instruction: <u>Two bytes following op code</u> specifies how far to branch

<u>Treat the offset as an unsigned number</u>; add the offset to the address following the current instruction to get the address of the instruction to branch to

(LBEQ) 18 27 02 1A If Z == 1 then PC + 4 + 021A  $\rightarrow$  PC If Z == 0 then PC + 4  $\rightarrow$  PC

When writing assembly language program, <u>you don't have to</u> <u>calculate offset</u>

You indicate what address you want to go to, and the assembler calculates the offset

| 0x2020 I | BRA  | \$2030 |    | ; Branch to instruction at<br>; address \$2030 |

|----------|------|--------|----|------------------------------------------------|

| 0x202    | 0 20 | ]      | PC | 2020                                           |

|          | 0E   | ]      |    |                                                |

# Summary of HCS12 addressing modes

# **ADDRESSING MODES**

| Name                |                          | Example                             | Op Code                          | Effective<br>Address               |

|---------------------|--------------------------|-------------------------------------|----------------------------------|------------------------------------|

| INH                 | Inherent                 | ABA                                 | 18 06                            | None                               |

| IMM                 | Immediate                | LDAA #\$35                          | 86 35                            | PC + 1                             |

| DIR                 | Direct                   | LDAA \$35                           | 96 35                            | 0x0035                             |

| EXT                 | Extended                 | LDAA \$2035                         | B6 20 35                         | 0x2035                             |

| IDX<br>IDX1<br>IDX2 | Indexed                  | LDAA 3,X<br>LDAA 30,X<br>LDAA 300,X | A6 03<br>A6 E0 13<br>A6 E2 01 2C | X + 3<br>X + 30<br>X + 300         |

| IDX                 | Indexed<br>Postincrement | ldaa 3, X+                          | A6 32                            | X (X+3 -> X)                       |

| IDX                 | Indexed<br>Preincrement  | ldaa 3,+x                           | A6 22                            | X+3 (X+3 -> X)                     |

| IDX                 | Indexed<br>Postdecrement | LDAA 3, X-                          | A6 3D                            | x (x-3 -> x)                       |

| IDX                 | Indexed<br>Predecrement  | ldaa 3,-x                           | A6 2D                            | X−3 (X−3 −> X)                     |

| REL                 | Relative                 | BRA \$1050<br>LBRA \$1F00           | 20 23<br>18 20 OE CF             | PC + 2 + Offset<br>PC + 4 + Offset |

# A few instructions have two effective addresses:

| • MOVB \$2000,\$3000 | ;move byte from address \$2000 to<br>;\$3000                            |

|----------------------|-------------------------------------------------------------------------|

| • MOVW 0,X,0,Y       | ;move word from address pointed to<br>; by X to address pointed to by Y |