### HC12 Addressing Modes

- Inherent, Extended, Direct, Immediate, Indexed, and Relative Modes

- Summary of MC9S12 Addressing Modes

- o Using X and Y registers as pointers

- How to tell which branch instruction to use

### Instruction coding and execution

- How to hand assemble a program

- Number of cycles and time taken to execute an MC9S12 program

### The MC9S12 has 6 addressing modes

Most of the HC12's instructions access data in memory There are several ways for the HC12 to determine which address to access

### **Effective address:**

Memory address used by instruction (all modes except INH)

### **Addressing mode:**

How the MC9S12 calculates the effective address

### **HC12 ADDRESSING MODES:**

**INH** Inherent

**IMM** Immediate

**DIR Direct**

**EXT Extended**

REL Relative (used only with branch instructions)

IDX Indexed (won't study indirect indexed mode)

## The Inherent (INH) addressing mode

Instructions which work only with registers inside ALU

ABA ; Add B to A  $(A) + (B) \rightarrow A$

18 06

CLRA ; Clear A  $0 \rightarrow A$

87

ASRA ; Arithmetic Shift Right A

47

TSTA ; Test A (A) - 0x00 Set CCR 97

The HC12 does not access memory

There is no effective address

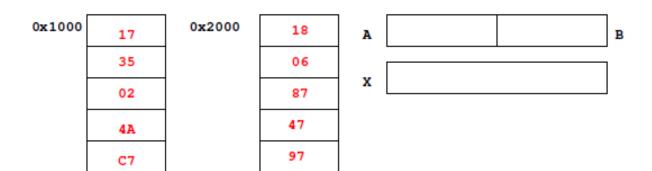

### The Extended (EXT) addressing mode

Instructions which give the 16-bit address to be accessed

LDAA \$1000 ; (\$1000)  $\rightarrow$  A

**B6 10 00** Effective Address: \$1000

LDX \$1001 ; (\$1001:\$1002)  $\rightarrow$  X

**FE 10 01** Effective Address: \$1001

STAB \$1003 ; (B)  $\rightarrow$  \$1003

**7B 10 03** Effective Address: \$1003

# Effective address is specified by the two bytes following op code

03

| 0X1000 | 17 | 0x2000 | В6 |

|--------|----|--------|----|

|        | 35 |        | 10 |

|        | 02 |        | 00 |

|        | 4A |        | FE |

|        | C7 |        | 10 |

|        |    |        | 01 |

|        |    |        | 7B |

|        |    |        | 10 |

|        |    |        |    |

| A |  | 1 |

|---|--|---|

| x |  |   |

| X |  |   |

### The Direct (DIR) addressing mode

Direct (DIR) Addressing Mode Instructions which give 8 LSB of address (8 MSB all 0)

LDAA \$20 ; (\$0020)  $\rightarrow$  A

**96 20** Effective Address: \$0020

STX \$21 ; (X)  $\rightarrow$  \$0021:\$0022

**5E 21** Effective Address: \$0021

8 LSB of effective address is specified by byte following op code

| 0x1000 | 17 | 0x0020 | 96 |

|--------|----|--------|----|

|        | 35 |        | 20 |

|        | 02 |        | 5E |

|        | 4A |        | 21 |

|        |    |        |    |

| A |  | 1 |

|---|--|---|

| x |  |   |

## The Immediate (IMM) addressing mode

Value to be used is part of instruction

LDAA #\$17 ;  $$17 \rightarrow A$

**B6 17** Effective Address: PC + 1

ADDA #10 ; (A) +  $\$0A \rightarrow A$

**8B 0A** Effective Address: PC + 1

Effective address is the address following the op code

| 0 <b>x</b> 1000 | 17 | 0x2000 | 86         |

|-----------------|----|--------|------------|

|                 | 35 |        | 17         |

|                 | 02 |        | 8B         |

|                 | 4A |        | 0 <b>A</b> |

|                 | с7 |        |            |

| A |   | 1 |

|---|---|---|

|   |   |   |

| x | 1 | ı |

### The Indexed (IDX, IDX1, IDX2) addressing mode

Effective address is obtained from X or Y register (or SP or PC) Simple Forms

LDAA 0,X ; Use (X) as address to get value to put in A

**A6 00** Effective address: contents of X

ADDA 5,Y; Use (Y) + 5 as address to get value to add

to

**AB 45** Effective address: contents of Y + 5

### More Complicated Forms

INC 2,X-; Post-decrement Indexed

; Increment the number at address (X),

; then subtract 2 from X

**62 3E** Effective address: contents of X

INC 4,+X ; Pre-increment Indexed

; Add 4 to X

; then increment the number at address (X)

**62 23** Effective address: contents of X + 4

Table 3-1. M68HC12 Addressing Mode Summary

| Addressing Mode                         | Source Format                                | Abbreviation | Description                                                                                                             |

|-----------------------------------------|----------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| Inherent                                | INST<br>(no externally<br>supplied operands) | INH          | Operands (if any) are in CPU registers                                                                                  |

| Immediate                               | INST #opr8i<br>or<br>INST #opr16i            | IMM          | Operand is included in instruction stream<br>8- or 16-bit size implied by context                                       |

| Direct                                  | INST opr8a                                   | DIR          | Operand is the lower 8 bits of an address<br>in the range \$0000–\$00FF                                                 |

| Extended                                | INST opr16a                                  | EXT          | Operand is a 16-bit address                                                                                             |

| Relative                                | INST rel8<br>or<br>INST rel16                | REL          | An 8-bit or 16-bit relative offset from the current pc<br>is supplied in the instruction                                |

| Indexed<br>(5-bit offset)               | INST oprx5,xysp                              | IDX          | 5-bit signed constant offset<br>from X, Y, SP, or PC                                                                    |

| Indexed (pre-decrement)                 | INST oprx3,-xys                              | IDX          | Auto pre-decrement x, y, or sp by 1 ~ 8                                                                                 |

| Indexed (pre-increment)                 | INST oprx3,+xys                              | IDX          | Auto pre-increment x, y, or sp by 1 ~ 8                                                                                 |

| Indexed (post-decrement)                | INST oprx3,xys=                              | IDX          | Auto post-decrement x, y, or sp by 1 ~ 8                                                                                |

| Indexed (post-increment)                | INST oprx3,xys+                              | IDX          | Auto post-increment x, y, or sp by 1 ~ 8                                                                                |

| Indexed<br>(accumulator offset)         | INST abd,xysp                                | IDX          | Indexed with 8-bit (A or B) or 16-bit (D)<br>accumulator offset from X, Y, SP, or PC                                    |

| Indexed<br>(9-bit offset)               | INST oprx9,xysp                              | IDX1         | 9-bit signed constant offset from X, Y, SP, or PC<br>(lower 8 bits of offset in one extension byte)                     |

| Indexed<br>(16-bit offset)              | INST oprx16,xysp                             | IDX2         | 16-bit constant offset from X, Y, SP, or PC (16-bit offset in two extension bytes)                                      |

| Indexed-Indirect<br>(16-bit offset)     | INST [oprx16,xysp]                           | [IDX2]       | Pointer to operand is found at<br>16-bit constant offset from X, Y, SP, or PC<br>(16-bit offset in two extension bytes) |

| Indexed-Indirect (D accumulator offset) | INST [D,xysp]                                | [D,IDX]      | Pointer to operand is found at<br>X, Y, SP, or PC plus the value in D                                                   |

# Different types of indexed addressing modes

(Note: We will not discuss indirect indexed mode)

### **INDEXED ADDRESSING MODES**

### (Does not include indirect modes)

|                 | Example                          | Effective<br>Address          | Offset                          | Value in X<br>After Done | Registers<br>To Use |

|-----------------|----------------------------------|-------------------------------|---------------------------------|--------------------------|---------------------|

| Constant Offset | LDAA n,X                         | (X)+n                         | 0 to FFFF                       | (X)                      | X, Y, SP, PC        |

| Constant Offset | IDAA -n, X                       | (X)-n                         | 0 to FFFF                       | (X)                      | X, Y, SP, PC        |

| Postingrement   | LDAA n, X+                       | (X)                           | 1 to 8                          | (X)+n                    | X, Y, SP            |

| Preincrement    | LDAA n,+X                        | (X)+n                         | 1 to 8                          | (X)+n                    | X, Y, SP            |

| Postdecrement   | LDAA n, X-                       | (X)                           | 1 to 8                          | (X)-n                    | X, Y, SP            |

| Predecrement    | LDAA n,-X                        | (X)-n                         | 1 to 8                          | (X)-n                    | X, Y, SP            |

| ACC Offset      | IDAA A,X<br>IDAA B,X<br>IDAA D,X | (X)+(A)<br>(X)+(B)<br>(X)+(D) | 0 to FF<br>0 to FF<br>0 to FFFF | (X)                      | X, Y, SP, PC        |

## The data books list three different types of indexed modes:

- Table 3.2 of the **S12CPUV2 Reference Manual** shows details

- **IDX**: One byte used to specify address

- Called the postbyte

- Tells which register to use

- Tells whether to use autoincrement or autodecrement

- Tells offset to use

- **IDX1:** Two bytes used to specify address

- First byte called the postbyte

- Second byte called the extension

- Postbyte tells which register to use, and sign of offset

- Extension tells size of offset

- **IDX2:** Three bytes used to specify address

- First byte called the postbyte

- Next two bytes called the extension

- Postbyte tells which register to use

- Extension tells size of offset

Table 3-2. Summary of Indexed Operations

| Postbyte<br>Code (xb) | Source<br>Code<br>Syntax  | Comments<br>rr; 00 = X, 01 = Y, 10 = SP, 11 = PC                                                                                                                                           |                                        |  |

|-----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| rrOnnnn               | n,r<br>n,r<br>n,r         | 5-bit constant offset n = -16 to +15<br>r can specify X, Y, SP, or PC                                                                                                                      |                                        |  |

| 111rr0zs              | n,r<br>–n,r               | Constant offset (9- or 16-bit signed) z- 0 = 9-bit with sign in LSB of postbyte(s) 1 = 16-bit if z = s = 1, 16-bit offset indexed-indirect (see below) r can specify X, Y, SP, or PC       | -256 ≤ n ≤ 255<br>-32,768 ≤ n ≤ 65,535 |  |

| 111rr011              | [n,r]                     | 16-bit offset indexed-indirect<br>rr can specify X, Y, SP, or PC                                                                                                                           | -32,768 ≤ n ≤ 65,535                   |  |

| rr1pnnnn              | n,-r n,+r<br>n,r-<br>n,r+ | Auto predecrement, preincrement, postdecrement, of p = pre-(0) or post-(1), n = -8 to -1, +1 to +8 r can specify X, Y, or SP (PC not a valid choice) +8 = 0111 +1 = 0000 -1 = 11118 = 1000 | r postincrement;                       |  |

| 111rr1aa              | A,r<br>B,r<br>D,r         | Accumulator offset (unsigned 8-bit or 16-bit) aa-00 = A 01 = B 10 = D (16-bit) 11 = see accumulator D offset indexed-indirect r can specify X, Y, SP, or PC                                |                                        |  |

| 111rr111              | [D,r]                     | Accumulator D offset indexed-indirect<br>r can specify X, Y, SP, or PC                                                                                                                     |                                        |  |

Indexed addressing mode instructions use a postbyte to specify index registers (X and Y), stack pointer (SP), or program counter (PC) as the base index register and to further classify the way the effective address is formed. A special group of instructions cause this calculated effective address to be loaded into an index register for further calculations:

- Load stack pointer with effective address (LEAS)

- Load X with effective address (LEAX)

- · Load Y with effective address (LEAY)

### **Relative (REL) Addressing Mode**

The relative addressing mode is used only in branch and long branch instructions.

Branch instruction: One byte following op code specifies how far to branch.

<u>Treat the offset as a signed number</u>; add the offset to the address following the current instruction to get the address of the instruction to branch to

**(BRA) 20 35** PC + 2 + 0035

$$\rightarrow$$

PC

(BRA) 20 C7 PC + 2 + FFC7

$$\rightarrow$$

PC

PC + 2 - 0039  $\rightarrow$  PC

Long branch instruction: Two bytes following op code specifies how far to branch.

<u>Treat the offset as an unsigned number</u>; add the offset to the address following the current instruction to get the address of the instruction to branch to

**(LBEQ) 18 27 02 1A** If

$$Z == 1$$

then  $PC + 4 + 021A \rightarrow PC$

If  $Z == 0$  then  $PC + 4 \rightarrow PC$

When writing assembly language program, you don't have to calculate offset. You indicate what address you want to go to, and the assembler calculates the offset

# Summary of MC9S12 addressing modes **ADDRESSING MODES**

| Na                  | me                       | Example                             | Op Code                          | Effective<br>Address               |

|---------------------|--------------------------|-------------------------------------|----------------------------------|------------------------------------|

| INH                 | Inherent                 | ABA                                 | 18 06                            | None                               |

| IMM                 | Immediate                | LDAA #\$35                          | 86 35                            | PC + 1                             |

| DIR                 | Direct                   | LDAA \$35                           | 96 35                            | 0x0035                             |

| EXT                 | Extended                 | LDAA \$2035                         | B6 20 35                         | 0x2035                             |

| IDX<br>IDX1<br>IDX2 | Indexed                  | LDAA 3,X<br>LDAA 30,X<br>LDAA 300,X | A6 03<br>A6 E0 13<br>A6 E2 01 2C | X + 3<br>X + 30<br>X + 300         |

| IDX                 | Indexed<br>Postincrement | LDAA 3,X+                           | A6 32                            | x (x+3 -> x)                       |

| IDX                 | Indexed<br>Preincrement  | LDAA 3,+X                           | A6 22                            | X+3 (X+3 -> X)                     |

| IDX                 | Indexed<br>Postdecrement | LDAA 3,X-                           | A6 3D                            | x (x-3 -> x)                       |

| IDX                 | Indexed<br>Predecrement  | LD <b>AA</b> 3,-X                   | A6 2D                            | x-3 (x-3 -> x)                     |

| REL                 | Relative                 | BRA \$1050<br>LBRA \$1F00           | 20 23<br>18 20 0E CF             | PC + 2 + Offset<br>PC + 4 + Offset |

### A few instructions have two effective addresses:

• MOVB #\$AA,\$1C00 Move byte 0xAA (IMM) to address

\$1C00 (EXT)

• **MOVW 0,X,0,Y** Move word from address pointed to by

X (IDX) to address pointed to by Y

(IDX)

### A few instructions have three effective addresses:

• **BRSET FOO,#\$03,LABEL** Branch to LABEL (REL) if bits #\$03 (IMM) of variable FOO (EXT) are set.

### Using X and Y as Pointers

- Registers X and Y are often used to point to data.

- To initialize pointer use

ldx #table

not

ldx table

• For example, the following loads the address of table (\$1000) into X; i.e., X will point to table:

**ldx** #table ; Address of table  $\Rightarrow X$

The following puts the first two bytes of table (\$0C7A) into X. X will not point to table:

**ldx table** ; *First two bytes of table*  $\Rightarrow X$

• To step through table, need to increment pointer after use

ldaa 0,x inx

or

ldaa 1,x+

|       | Data                 | Address                              |        |                             |                                      |

|-------|----------------------|--------------------------------------|--------|-----------------------------|--------------------------------------|

| table | 0C<br>7A<br>D5<br>00 | \$1000<br>\$1001<br>\$1002<br>\$1003 | table: | org<br>dc.b<br>dc.b<br>dc.b | \$1000<br>12,122,-43,0<br>'a'<br>'b' |

|       | 61<br>62<br>63<br>64 | \$1004<br>\$1005<br>\$1006<br>\$1007 |        | dc.b<br>dc.b                | ' c'<br>' d'                         |

### Which branch instruction should you use?

Branch if A > B

Is 0xFF > 0x00?

If unsigned, 0xFF = 255 and 0x00 = 0, so 0xFF > 0x00

If signed, 0xFF = -1 and 0x00 = 0, so 0xFF < 0x00

Using unsigned numbers: **BHI** (checks C bit of CCR)

Using signed numbers: **BGT** (checks V bit of CCR)

For unsigned numbers, use branch instructions which check C bit

For signed numbers, use branch instructions which check V bit

### **Hand Assembling a Program**

To hand-assemble a program, do the following:

- **1**. Start with the **org** statement, which shows where the first byte of the program will go into memory. (e.g., **org** \$2000 will put the first instruction at address \$2000.)

- **2**. Look at the first instruction. Determine the addressing mode used.

(e.g., **ldab** #10 uses IMM mode.)

- **3**. Look up the instruction in the **MC9S12 S12CPUV2 Reference Manual**, find the appropriate Addressing Mode, and the Object Code for that addressing mode. (e.g., **ldab IMM** has object code **C6 ii**.)

- Table A.1 of S12CPUV2 Reference Manual has a concise summary of the instructions, addressing modes, op-codes, and cycles.

- **4**. Put in the object code for the instruction, and put in the appropriate operand. Be careful to convert decimal operands to hex operands if necessary. (e.g., **ldab** #10 becomes **C6** 0**A**.)

- **5.** Add the number of bytes of this instruction to the address of the instruction to determine the address of the next instruction. (e.g., \$2000 + 2 = \$2002 will be the starting address of the next instruction.)

# Freescale HC12-Assembler (c) Copyright Freescale 1987-2010

### Abs. Rel. Loc Obj. code Source line

| 1 | 1 |                 |       |      |        |

|---|---|-----------------|-------|------|--------|

| 2 | 2 | 0000 2000       | prog: | equ  | \$2000 |

| 3 | 3 |                 |       | org  | prog   |

| 4 | 4 | a002000 C60A    |       | ldab | #10    |

| 5 | 5 | a002002 87      | loop: | clra |        |

| 6 | 6 | a002003 0431 FC |       | dbne | b,loop |

| 7 | 7 | a002006 3F      |       | swi  |        |

# What the corresponding assembly code?

org \$2000 ldab #10 loop: clra dbne b,loop swi

#### Table A-1. Instruction Set Summary (Sheet 7 of 14)

|                                                                                                                                                       | 1                                                                               | Addr.                                                         | Machine                                                                                      | Anne                                                       | os Dotail                                                  |      |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|------|------|

| Source Form                                                                                                                                           | Operation                                                                       | Mode                                                          | Coding (hex)                                                                                 | HCS12                                                      | M68HC12                                                    | SXHI | NZVC |

| LBGT raft 6                                                                                                                                           | Long Branch if Greater Than<br>(if $Z + (N \oplus V) = 0$ ) (signed)            | REL                                                           | 18 2E qq rr                                                                                  | 0999/090 <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBHI rehs                                                                                                                                             | Long Branch if Higher<br>(if C + Z = 0) (unsigned)                              | REL                                                           | 18 22 qq rr                                                                                  | OPPP/OPOI                                                  | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBHS rah 6                                                                                                                                            | Long Branch if Higher or Same<br>(if C = 0) (unsigned)<br>same function as LBCC | REL                                                           | 18 24 qq rr                                                                                  | 0999/090 <sup>1</sup>                                      | 0PPP/0P0 <sup>1</sup>                                      |      |      |

| LBLE rah 6                                                                                                                                            | Long Branch if Less Than or Equal<br>(if $Z + (N \oplus V) = 1$ ) (signed)      | REL                                                           | 18 2F qq rr                                                                                  | 0999/0901                                                  | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBLOwhs                                                                                                                                               | Long Branch if Lower<br>(fl C = 1) (unsigned)<br>same function as LBCS          | REL                                                           | 18 25 qq rr                                                                                  | OPPP/OPO <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBLS rah 6                                                                                                                                            | Long Branch if Lower or Same<br>(if C + Z = 1) (unsigned)                       | REL                                                           | 18 23 qq rr                                                                                  | 0555/0501                                                  | OPPP/OPO*                                                  |      |      |

| LBLT re/h6                                                                                                                                            | Long Branch if Less Than<br>(if N ⊕ V = 1) (signed)                             | REL                                                           | 18 2D qq rr                                                                                  | 0555/0501                                                  | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBMI ral 18                                                                                                                                           | Long Branch if Minus (if N = 1)                                                 | REL                                                           | 18 2B qq rr                                                                                  | 0999/0901                                                  | OPPP/OPO1                                                  |      |      |

| LBNE ralt 6                                                                                                                                           | Long Branch if Not Equal (if Z = 0)                                             | REL                                                           | 18 26 qq rr                                                                                  | oppp/opo <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBPL raft 6                                                                                                                                           | Long Branch if Plus (if N = 0)                                                  | REL                                                           | 18 2A qq rr                                                                                  | 0999/090 <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBRA rah 6                                                                                                                                            | Long Branch Always (f 1-1)                                                      | REL                                                           | 18 20 qq rr                                                                                  | OPPP                                                       | OPPP                                                       |      |      |

| LBRN ral 16                                                                                                                                           | Long Branch Never (f 1 = 0)                                                     | REL                                                           | 18 21 qq rr                                                                                  | OPO                                                        | OPO                                                        |      |      |

| LBVC raft 6                                                                                                                                           | Long Branch if Overflow Bit Clear (if V=0)                                      | REL                                                           | 18 28 qq rr                                                                                  | 0999/0901                                                  | OPPP/OPO <sup>1</sup>                                      |      |      |

| LBVS relte                                                                                                                                            | Long Branch if Overflow Bit Set (if V = 1)                                      | REL                                                           | 18 29 qq rr                                                                                  | oppp/opo <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                      |      |      |

| LDAA aprilia<br>LDAA oprilia<br>LDAA oprilia<br>LDAA oprilia<br>LDAA oprilia<br>LDAA oprilia<br>LDAA [Daysp]<br>LDAA [Daysp]<br>LDAA [Daysp]          | (M) → A<br>Load Accumulator A                                                   | IMM DIR EXT IDX IDX: IDX2 [D,IDX]                             | 86 11<br>96 dd<br>B6 hh 11<br>A6 xb<br>A6 xb ff<br>A6 xb ee ff<br>A6 xb ee ff<br>A6 xb ee ff | p<br>rpf<br>rpo<br>rpf<br>rpo<br>frpp<br>fifrpf<br>fiprpf  | 9<br>rf9<br>r09<br>rf9<br>r90<br>fr99<br>frfrf9<br>frfrf9  |      | ΔΔ0- |

| LDAB #opr8i LDAB gor8a LDAB opr1 8a LDAB opr01 xysp LDAB opr01 xysp LDAB opr01 xysp LDAB (Dxysp) LDAB [Dxysp) LDAB [Dxysp] LDAB [Dxysp]               | (M) → B<br>Load Accumulator B                                                   | IMM<br>DIR<br>EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]           | C6 11<br>D6 dd<br>F6 hh 11<br>E6 xb<br>E6 xb ff<br>E6 xb ec ff<br>E6 xb ec ff<br>E6 xb ec ff | P<br>rPf<br>rPO<br>rPf<br>rPO<br>frPP<br>fIfrPf<br>fIPrPf  | p<br>rfp<br>r09<br>rfp<br>r90<br>fr99<br>frfrfp            |      | ΔΔ0- |

| LDD #opr16i LDD opr18a LDD opr18a LDD opr18a LDD opr08, xysp LDD opr08, xysp LDD opr018, xysp LDD (Dpr018, xysp LDD (Dpr018, xysp) LDD [opr018, xysp] | (M:M+1) → A:B<br>Load Double Accumulator D (A:B)                                | IMM<br>DIR<br>EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]<br>[IDX2] | CC jj kk DC dd PC hh 11 EC xb EC xb ff EC xb se ff EC xb se ff                               | PO<br>RPE<br>RPO<br>RPE<br>RPO<br>EMPP<br>EIERPE<br>EIPRPE | OP<br>REP<br>ROP<br>REP<br>RPO<br>ERPP<br>EIEREP<br>EIEREP |      | ΔΔ0- |

Note 1. OPPPIOPO indicates this instruction takes four cycles to refill the instruction quaue if the branch is taken and three cycles if the branch is not taken.

Table A-1. Instruction Set Summary (Sheet 3 of 14)

|                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                      | Addr.                                                         | Machine                                                                          | Access De                                                                           | tail                                                                      |      |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|

| Source Form                                                                                                                                        | Operation                                                                                                                                                                                                                                                                                                                                            | Mode                                                          | Coding (hex)                                                                     | HCS12                                                                               | M68HC12                                                                   | SXHI | NZVC |

| BLS no.18                                                                                                                                          | Branch if Lower or Same<br>(if C + Z = 1) (unsigned)                                                                                                                                                                                                                                                                                                 | REL                                                           | 23 rr                                                                            | PPP/p <sup>1</sup>                                                                  | PPP/p <sup>1</sup>                                                        |      |      |

| BLT rale                                                                                                                                           | Branch if Less Than<br>(if N ⊕ V = 1) (signed)                                                                                                                                                                                                                                                                                                       | REL                                                           | 2D rr                                                                            | PPP/pl                                                                              | ppp/pl                                                                    |      |      |

| BMI ral8                                                                                                                                           | Branch if Minus (if N = 1)                                                                                                                                                                                                                                                                                                                           | REL                                                           | 2B rr                                                                            | ppp/pl                                                                              | PPP/p <sup>1</sup>                                                        |      |      |

| BNE rol8                                                                                                                                           | Branch if Not Equal (if Z = 0)                                                                                                                                                                                                                                                                                                                       | REL                                                           | 26 rr                                                                            | ppp/p <sup>1</sup>                                                                  | ppp/p <sup>1</sup>                                                        |      |      |

| BPL note                                                                                                                                           | Branch if Plus (if N = 0)                                                                                                                                                                                                                                                                                                                            | REL                                                           | 2A rr                                                                            | ppp/p <sup>1</sup>                                                                  | ppp/p <sup>1</sup>                                                        |      |      |

| BRAnolis                                                                                                                                           | Branch Always (if 1 – 1)                                                                                                                                                                                                                                                                                                                             | REL                                                           | 20 rr                                                                            | PPP                                                                                 | PPP                                                                       |      |      |

| BRCLR oprila, msk8, ralb<br>BRCLR oprila, msk8, ralb<br>BRCLR oprila, rysp, msk8, ralb<br>BRCLR oprila, rysp, msk8, ralb                           | Branch if (M) • (mm) = 0<br>(if All Selected Bh(s) Clear)                                                                                                                                                                                                                                                                                            | DIR<br>EXT<br>IDX<br>IDX1                                     | 4F dd mm rr<br>1F hh 11 mm rr<br>0F xb mm rr<br>0F xb ff mm rr                   | ####<br>#####<br>####<br>#####                                                      | rPPP<br>rfPPP<br>rPPP<br>rffPPP                                           |      |      |

| BRCLR o'pox16,xyisp, msk8, ral8<br>BRN ral8                                                                                                        | Describ Name (6.4. a)                                                                                                                                                                                                                                                                                                                                | IDX2<br>REL                                                   | OF xb ee ff mm rr                                                                | Prfppp                                                                              | ErpEEppp                                                                  |      |      |

| BRSET opr8, msk8, ral8                                                                                                                             | Branch Never (f 1 = 0)                                                                                                                                                                                                                                                                                                                               | DIR                                                           | 21 rr<br>4E dd mm rr                                                             | 2<br>2<br>2<br>2<br>2                                                               | rPPP                                                                      |      |      |

| BRSET april (in maks, nale<br>BRSET april (in maks, nale<br>BRSET april (in maks, nale<br>BRSET april (in maks, nale<br>BRSET april (in maks, nale | Branch if (M) • (mm) = 0<br>(if All Selected Bit(s) Set)                                                                                                                                                                                                                                                                                             | EXT<br>IDX<br>IDX1<br>IDX2                                    | 1E hh 11 mm rr<br>0E xb mm rr<br>0E xb ff mm rr<br>0E xb Ge ff mm rr             | repor<br>repor<br>repor<br>repor<br>prepor                                          | rfppp<br>rppp<br>rffppp<br>rffppp<br>frpffppp                             |      |      |

| BSET opr8, msk8<br>BSET opr16u, msk8<br>BSET opr00_xysp, msk8<br>BSET opr01/xysp, msk8<br>BSET opr016,xysp, msk8                                   | (M) + (mm) → M<br>Set Bit(s) in Memory                                                                                                                                                                                                                                                                                                               | DIR<br>EXT<br>IDX<br>IDX1<br>IDX2                             | 4C dd mm<br>1C hh 11 mm<br>0C xb mm<br>0C xb ff mm<br>0C xb ee ff mm             | rPw0<br>rPw0<br>rPw0<br>rPw0<br>frPw00                                              | rPOw<br>rPOw<br>rPOw<br>rPw0<br>ErPw0P                                    |      | ΔΔ0- |

| BSR reals                                                                                                                                          | (SP) - 2 → SP; RTN <sub>E</sub> RTN <sub>L</sub> → M <sub>SP</sub> ;M <sub>(SP+1)</sub><br>Subroutine address → PC<br>Branch to Subroutine                                                                                                                                                                                                           | REL                                                           | 07 rr                                                                            | SPPP                                                                                | PPPS                                                                      |      |      |

| BVC red8                                                                                                                                           | Branch if Overflow Bit Clear (if V = 0)                                                                                                                                                                                                                                                                                                              | REL                                                           | 28 rr                                                                            | ppp/p <sup>1</sup>                                                                  | ppp/p <sup>1</sup>                                                        |      |      |

| BVS ral8                                                                                                                                           | Branch if Overflow Bit Set (if V = 1)                                                                                                                                                                                                                                                                                                                | REL                                                           | 29 rr                                                                            | ppp/p <sup>1</sup>                                                                  | PPP/p <sup>1</sup>                                                        |      |      |

| CALL oprifilis, page CALL [D.xysp] CALL [Oprifilis, xysp]      | (SP) − 2 → SP; RTN <sub>sc</sub> RTN <sub>1</sub> → M <sub>SPp</sub> ;M <sub>(SP+1)</sub> (SP) − 1 → SP; (SPG) → M <sub>SPp</sub> ; pg → PPAGE register; Program address → PC  Call subrovitine in extended memory (Program may be located on another expansion memory page.)  Indirect modes get program address and new pg value based on pointer. | EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]<br>[IDX2]               | 4A hh 11 pg<br>4B xb pg<br>4B xb ff pg<br>4B xb ee ff pg<br>4B xb<br>4B xb ee ff | gndappp<br>gndappp<br>gndappp<br>fgndappp<br>fligndappp<br>fligndappp<br>fligndappp | gnfSePPP<br>gnfSePPP<br>gnfSePPP<br>fgnfSePPP<br>flignSePPP<br>flignSePPP |      |      |

| CBA                                                                                                                                                | (A) – (B)<br>Compare 8-Bit Accumulators                                                                                                                                                                                                                                                                                                              | INH                                                           | 18 17                                                                            | 00                                                                                  | 00                                                                        |      | ΔΔΔΔ |

| CTC                                                                                                                                                | 0 → C Translates to ANDCC #\$FE                                                                                                                                                                                                                                                                                                                      | IMM                                                           | 10 FE                                                                            | P                                                                                   | P                                                                         |      | 0    |

| CLI                                                                                                                                                | 0 → 1 Translates to ANDCC #\$EF (enables I-bit interrupts)                                                                                                                                                                                                                                                                                           | IMM                                                           | 10 EF                                                                            | P                                                                                   | P                                                                         | 0    |      |

| CLR opriSu CLR oprazi, xysp CLR oprazi, xysp CLR oprazi, xysp CLR [D, xysp] CLR [D, xysp] CLR [CLR CLR CLR CLR CLR CLR CLR CLR CLR CLR             | 0 → M Clear Memory Location  0 → A Clear Accumulator A  0 → B Clear Accumulator B                                                                                                                                                                                                                                                                    | EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]<br>[IDX2]<br>INH<br>INH | 79 hh 11<br>69 xb<br>69 xb ff<br>69 xb ee ff<br>69 xb ee ff<br>87<br>C7          | PwO<br>Pw<br>PwO<br>PwS<br>PIFw<br>PIFw<br>O<br>O                                   | WOP<br>PWO<br>PWO<br>PIEPW<br>PIEPW<br>O<br>O                             |      | 0100 |

| CLV                                                                                                                                                | 0 → V Translates to ANDCC #\$FD                                                                                                                                                                                                                                                                                                                      | IMM                                                           | 10 FD                                                                            | P                                                                                   | P                                                                         |      | 0-   |

Note 1. PPPIP indicates this instruction takes three cycles to refit the instruction queue if the branch is taken and one program fetch cycle if the branch is not taken.

Table A-1. Instruction Set Summary (Sheet 4 of 14)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                                                                                                                                                                                    |                                                               |                                                                                                 |                                    |                                                |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------|------|------|

| Source Form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Operation                                                                                                                                                                                            | Addr.<br>Mode                                                 | Machine<br>Coding (hex)                                                                         | Access Detail<br>HCS12 MG          | HC12                                           | SXHI | NZVC |

| CMFB #opr8i CMFB opr8e CMFB opr16e CMFB opr16e CMFB opr02, y/sp CMFB opr02, y/sp CMFB opr04, y/sp CMFB (opr04, y/sp CMFB [0, y/sp) CMFB [0, y/sp] CMFB [0, y/sp]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (B) – (M)<br>Compare Accumulator B with Memory                                                                                                                                                       | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [DX2]                       | C1 ii D1 dd F1 hh 11 E1 xb E1 xb ff E1 xb ee ff E1 xb ee ff E1 xb ee ff                         |                                    | rfp<br>r0p<br>rfp<br>rp0<br>frpp<br>frfp       |      | ΔΔΔΔ |

| COM oprifies COM opriol ayap COM opriol ayap COM priol ayap COM [D.ayap] COM [D.ayap] COM [don't E.ayap] COMA COMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (M) → M equivalent to \$FF − (M) → M 1's Complement Memory Location  (A) → A Complement Accumulator A (B) → B Complement Accumulator B                                                               | EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]<br>[IDX2]<br>INH<br>INH | 71 hh 11<br>61 xb<br>61 xb ff<br>61 xb ee ff<br>61 xb ee ff<br>61 xb ee ff<br>41<br>51          | fIfrPw fi                          | rOPe<br>rPe<br>rPOe<br>rPPe<br>frPe<br>0<br>0  |      | ΔΔ01 |

| CPD sepritif CPD opersu CPD (Dystep) CPD [Opersu CPD [Opersu CPD] | (A:B) – (M:M+1)<br>Compare D to Membry (16-Bit)                                                                                                                                                      | IMM<br>DIR<br>EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]<br>[DX2]  | BC jj kk<br>9C dd<br>BC hh 11<br>AC xb<br>AC xb ff<br>AC xb ee ff<br>AC xb<br>AC xb ee ff       |                                    | OF<br>REP<br>ROP<br>REP<br>RPO<br>ERPP<br>EREP |      | ΔΔΔΔ |

| CPS #cpr1 6i CPS opr8u CPS opr8u CPS opr8e CPS opr80, xysep CPS oprx 6, xysep CPS oprx 16, xysep CPS (D, xysep) CPS (D, xysep) CPS (D, xysep)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (SP) - (MtM+1)<br>Compare SP to Memory (16-Bit)                                                                                                                                                      | IMM<br>DIR<br>EXT<br>IDX<br>IDX1<br>IDX2<br>[D,IDX]<br>[IDX2] | 8F jj kk<br>9F dd<br>9F dd<br>AF xb<br>AF xb ff<br>AF xb ee ff<br>AF xb ee ff<br>AF xb ee ff    |                                    | OF<br>REP<br>ROP<br>REP<br>RPO<br>ERPP<br>EREP |      | ΔΔΔΔ |

| CPX exprt 6i CPX opr8a CPX opr18a CPX opr18a CPX opr02, xyep CPX opr02, xyep CPX oprx18, xyep CPX (D, xyep) CPX [D, xyep] CPX [D, xyep]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (X) – (M-M+1)<br>Compare X to Memory (16-Bit)                                                                                                                                                        | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [IDX2]                      | BE jj kk<br>9E dd<br>BE hh 11<br>AE xb<br>AE xb ff<br>AE xb ge ff<br>AE xb ge ff<br>AE xb ge ff |                                    | OF<br>REF<br>ROF<br>REF<br>RPO<br>ERFF<br>EREF |      | ΔΔΔΔ |

| CPY sopri 6i CPY oprise CPY oprise CPY oprise CPY oprise, xysp CPY oprise, xysp CPY oprise, xysp CPY oprise, xysp CPY (D, xysp) CPY [D, xysp] CPY [D, xysp]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (Y) – (M-M+1)<br>Compare Y to Memory (16-Bit)                                                                                                                                                        | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [IDX2]                      | 8D jj kk<br>9D dd<br>HD hh 11<br>AD xb<br>AD xb ff<br>AD xb se ff<br>AD xb<br>AD xb se ff       | EIPRPE EI                          | OF<br>REP<br>ROP<br>REP<br>RPO<br>ERPP<br>EREP |      | ΔΔΔΔ |

| DBEQ abdiyis, rolib                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Adjust Sum to BCD Docimal Adjust Accumulator A  (ontr) – 1 -> ontr  if (ontr) – 0, then Branch else Continue to next instruction  Decrement Counter and Branch if – 0  (ontr – A, B, D, X, Y, or SP) | REL<br>(9-bit)                                                | 18 07<br>04 lb rr                                                                               | OFO  PFF (branch)  PFO (no branch) | PPP                                            |      |      |

| DBNE abdays, rel9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (ont) = 1 so ont:  If (ont) not = 0, then Branch; else Continue to next instruction  Decrement Counter and Branch if ≠ 0 (ontr = A, B, D, X, Y, or SP)                                               | REL<br>(s-bit)                                                | 04 lb rr                                                                                        | PPP (branch)<br>PPO (no<br>branch) | PPP                                            |      |      |

### MC9S12 Cycles

- 68HC12 works on 48 MHz clock

- A processor cycle takes 2 clock cycles –P clock is 24 MHz

- Each processor cycle takes **41.7 ns** (1/24 MHz) to execute

- An instruction takes from **1** to **12** processor cycles to execute

- You can determine how many cycles an instruction takes by looking up the CPU cycles for that instruction in the S12CPUV2 Core Users Guide.

- For example, **LDAA** using the **IMM** addressing mode shows one CPU cycle (of type P).

- − **LDAA** using the **EXT** addressing mode shows three CPU cycles (of type **rPO**).

- Section 6.6 of the S12CPUV2 Reference Manual explains what the MC9S12 is doing during each of the different types of CPU cycles.

```

2000

org $2000

; Inst

Mode

Cycles

2000 C6 0A

ldab #10

; LDAB (IMM)

1

2002 87

loop: clra

; CLRA (INH)

1

2003 04 31 FC

dbne b,loop ; DBNE (REL)

3

2006 3F

; SWI

9

swi

```

How many cycles does it take? How long does it take to execute?

The program executes the **ldab** #10 instruction **once** (which takes one cycle). It then goes through loop 10 times (which has two instructions, one with one cycle and one with three cycles), and finishes with the swi instruction (which takes 9 cycles).

Total number of cycles:

$$1 + 10 \times (1 + 3) + 9 = 50$$

$$50 \text{ cycles} = 50 \times 41.7 \text{ ns/cycle} = 2.08 \ \mu\text{s}$$

LDAB

Load B

**LDAB**

Operation  $(M) \Rightarrow B$

ог

$imm \Rightarrow B$

Loads B with either the value in M or an immediate value.

CCR

Effects

| S | X | Н | I | N | Z | ٧ | С |

|---|---|---|---|---|---|---|---|

| - | - | • | - | Δ | Δ | 0 | - |

N: Set if MSB of result is set; cleared otherwise

Z: Set if result is \$00; cleared otherwise

V: Cleared

Code and CPU Cycles

| Source Form                                                                                                                                         | Address<br>Mode                          | Machine<br>Code (Hex)                                       | CPU Cycles                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------|--------------------------------------|

| LDAB #opr8i LDAB opr8a LDAB opr16a LDAB oprx0_xysppc LDAB oprx9,xysppc LDAB oprx16,xysppc LDAB [D,xysppc] LDAB [Oprx16,xysppc] LDAB [Oprx16,xysppc] | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [IDX2] | C6 ii D6 dd F6 hh ll E6 xb E6 xb ff E6 xb ee ff E6 xb ee ff | P rPf rPO rPf rPO frPP fIfrPf fIPrPf |

**CLRA**

Clear A

**CLRA**

Operation:  $0 \Rightarrow A$

Description: All bits in accumulator A are cleared to 0.

CCR Details:

| S | Х | Н | - 1 | N | Z | V | C |

|---|---|---|-----|---|---|---|---|

| - | - | - | -   | 0 | 1 | 0 | 0 |