- MC9S12 Assembler Directives

- A Summary of MC9S12 Instructions

- Disassembly of MC9S12 op codes

- Review of Addressing Modes

- Which branch instruction to use (signed vs unsigned)

- Using X and Y registers as pointers

- Hand assembling a program

- o How long does a program take to run?

- Assembler directives

- How to disassemble an MC9S12 instruction sequence

# Summary of HCS12 addressing modes

### **ADDRESSING MODES**

| Name                |                          | Example                             | Op Code                          | Effective<br>Address               |

|---------------------|--------------------------|-------------------------------------|----------------------------------|------------------------------------|

| INH                 | Inherent                 | ABA                                 | 18 06                            | None                               |

| IMM                 | Immediate                | LDAA #\$35                          | 86 35                            | PC + 1                             |

| DIR                 | Direct                   | LDAA \$35                           | 96 35                            | 0x0035                             |

| EXT                 | Extended                 | LDAA \$2035                         | B6 20 35                         | 0x2035                             |

| IDX<br>IDX1<br>IDX2 | Indexed                  | LDAA 3,X<br>LDAA 30,X<br>LDAA 300,X | A6 03<br>A6 E0 13<br>A6 E2 01 2C | X + 3<br>X + 30<br>X + 300         |

| IDX                 | Indexed<br>Postincrement | LDAA 3,X+                           | A6 32                            | x (x+3 -> x)                       |

| IDX                 | Indexed<br>Preincrement  | LDAA 3,+X                           | A6 22                            | X+3 (X+3 -> X)                     |

| IDX                 | Indexed<br>Postdecrement | LDAA 3,X-                           | A6 3D                            | x (x-3 -> x)                       |

| IDX                 | Indexed<br>Predecrement  | LDAA 3,-X                           | A6 2D                            | X-3 (X-3 -> X)                     |

| REL                 | Relative                 | BRA \$1050<br>LBRA \$1F00           | 20 23<br>18 20 0E CF             | PC + 2 + Offset<br>PC + 4 + Offset |

### A few instructions have two effective addresses:

• **MOVB #\$AA,\$1C00** Move byte 0xAA (IMM) to address

\$1C00 (EXT)

• **MOVW 0,X,0,Y** Move word from address pointed to by

X (IDX) to address pointed to by Y

(IDX)

### A few instructions have three effective addresses:

• **BRSET FOO,#\$03,LABEL** Branch to LABEL (REL) if bits #\$03 (IMM) of variable FOO (EXT) are set.

# Using X and Y as Pointers

- Registers X and Y are often used to point to data.

- To initialize pointer use

ldx #table

not

ldx table

• For example, the following loads the address of table (\$1000) into X; i.e., X will point to table:

**ldx** #table ; *Address of table*  $\Rightarrow$  *X*

The following puts the first two bytes of table (\$0C7A) into X. X will **not** point to table:

**ldx table** ; *First two bytes of table*  $\Rightarrow X$

• To step through table, need to increment pointer after use

ldaa 0,x inx

or

ldaa 1,x+

table 0C 7A D5 00 61 62

table: dc.b 12,122,-43,0 dc.b 'a','b','c','d'

# Which branch instruction should you use?

Branch if A > BIs 0xFF > 0x00?

If unsigned, 0xFF = 255 and 0x00 = 0, so 0xFF > 0x00

If signed, 0xFF = -1 and 0x00 = 0, so 0xFF < 0x00

Using unsigned numbers: **BHI** (checks C bit of CCR)

Using signed numbers: **BGT** (checks V bit of CCR)

For unsigned numbers, use branch instructions which check C bit

For signed numbers, use branch instructions which check V bit

**EE 308**

### **Hand Assembling a Program**

To hand-assemble a program, do the following:

- 1. Start with the org statement, which shows where the first byte of the program will go into memory.

- (e.g., **org** \$2000 will put the first instruction at address \$2000.)

- **2**. Look at the first instruction. Determine the addressing mode used.

- (e.g., **ldab** #**10** uses IMM mode.)

- 3. Look up the instruction in the MC9S12 S12CPUV2 Reference **Manual**, find the appropriate Addressing Mode, and the Object Code for that addressing mode. (e.g., **ldab IMM** has object code **C6 ii.)**

- Table A.1 of the S12CPUV2 Reference Manual has a concise summary of the instructions, addressing modes, op-codes, and cycles.

- **4.** Put in the object code for the instruction, and put in the appropriate operand. Be careful to convert decimal operands to hex operands if necessary. (e.g., **ldab** #10 becomes **C6 0A**.)

- **5.** Add the number of bytes of this instruction to the address of the instruction to determine the address of the next instruction. (e.g., \$2000 + 2 = \$2002 will be the starting address of the next instruction.)

org \$2000 ldab #10 loop: clra

dbne b,loop

swi

Freescale HC12-Assembler (c) Copyright Freescale 1987-2010

### Abs. Rel. Loc Obj. code Source line

1 1 2 2 0000 2000 prog: equ \$2000 3 3 org prog 4 a002000 C60A ldab #10 5 a002002 87 loop: clra 6 a002003 0431 FC dbne b,loop 7 a002006 3F swi

Table A-1. Instruction Set Summary (Sheet 7 of 14)

|                                                                                                                                                                                           |                                                                                 | Addr.                                    | Machine                                                                                      |                                                            | Access Detail                                                  |      |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|------|------|

| Source Form                                                                                                                                                                               | Operation                                                                       | Mode                                     | Coding (hex)                                                                                 | HCS12                                                      | M68HC12                                                        | SXHI | NZVC |

| LBGT rah 6                                                                                                                                                                                | Long Branch if Greater Than<br>(if $Z + (N \oplus V) = 0$ ) (signed)            | REL                                      | 18 2E qq rr                                                                                  | OPPP/OPO <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBHI rohe                                                                                                                                                                                 | Long Branch if Higher<br>(if C + Z = 0) (unsigned)                              | REL                                      | 18 22 qq rr                                                                                  | OPPP/OPOl                                                  | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBHS raft 6                                                                                                                                                                               | Long Branch if Higher or Same<br>(if C = 0) (unsigned)<br>same function as LBCC | REL                                      | 18 24 qq rr                                                                                  | 0999/0901                                                  | 0PPP/0PO <sup>1</sup>                                          |      |      |

| LBLE raft 6                                                                                                                                                                               | Long Branch if Less Then or Equal<br>(if $Z + (N \oplus V) = 1$ ) (signed)      | REL                                      | 18 2F qq rr                                                                                  | OPPP/OPOl                                                  | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBLO rehs                                                                                                                                                                                 | Long Branch if Lower<br>(if C = 1) (unsigned)<br>same function as LBCS          | REL                                      | 18 25 qq rr                                                                                  | 0999/0901                                                  | 0PPP/0PO <sup>1</sup>                                          |      |      |

| LBLS rah e                                                                                                                                                                                | Long Branch if Lower or Same<br>(if C + Z = 1) (unsigned)                       | REL                                      | 18 23 qq rr                                                                                  | OPPP/OPO <sup>1</sup>                                      | OPPP/OPO*                                                      |      |      |

| LBLT reh6                                                                                                                                                                                 | Long Branch if Less Than<br>(if N ⊕ V = 1) (signed)                             | REL                                      | 18 2D qq rr                                                                                  | OPPP/OPOl                                                  | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBMI rel 18                                                                                                                                                                               | Long Branch if Minus (if N = 1)                                                 | REL                                      | 18 2B qq rr                                                                                  | OFFF/OFO <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBNE ralt 6                                                                                                                                                                               | Long Branch if Not Equal (if Z = 0)                                             | REL                                      | 18 26 qq rr                                                                                  | OPPP/OPO <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBPL raft 6                                                                                                                                                                               | Long Branch if Plus (if N = 0)                                                  | REL                                      | 18 2A qq rr                                                                                  | OPPP/OPO <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBRA raft 6                                                                                                                                                                               | Long Branch Always (f 1-1)                                                      | REL                                      | 18 20 qq rr                                                                                  | OPPP                                                       | OPPP                                                           |      |      |

| LBRN ral 16                                                                                                                                                                               | Long Branch Never (f 1 = 0)                                                     | REL                                      | 18 21 qq rr                                                                                  | 090                                                        | OPO                                                            |      |      |

| LBVC raft 6                                                                                                                                                                               | Long Branch if Overflow Bit Clear (if V=0)                                      | REL                                      | 18 28 qq rr                                                                                  | OFFF/OFO <sup>1</sup>                                      | OPPP/OPO <sup>1</sup>                                          |      |      |

| LBVS rehts                                                                                                                                                                                | Long Branch if Overflow Bit Set (if V = 1)                                      | REL                                      | 18 29 qq rr                                                                                  | OPPP/OPO <sup>1</sup>                                      | орру/оро1                                                      |      |      |

| LDAA apprai<br>LDAA opraa<br>LDAA opraa xysp<br>LDAA opraa xysp<br>LDAA opraa xysp<br>LDAA opraa xysp<br>LDAA (pysp)<br>LDAA (pysp)<br>LDAA (pysa)                                        | (M) → A<br>Load Accumulator A                                                   | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [IDX2] | 86 11<br>96 dd<br>86 hh 11<br>A6 xb<br>A6 xb ff<br>A6 xb ff<br>A6 xb ee ff<br>A6 xb          | P                                                          | 9<br>169<br>109<br>169<br>190<br>1181<br>1191                  |      | ΔΔ0- |

| LDAB stopnel LDAB operio LDAB operio LDAB operio LDAB operio LDAB operio LDAB operio LDAB (D.xysp) LDAB (D.xysp) LDAB (D.xysp) LDAB (D.xysp) LDAB (operio LDAB (operio LDAB (operio LDAB) | (M) → B<br>Load Accumulator B                                                   | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [IDX2] | C6 11<br>D6 dd<br>F6 hh 11<br>E6 xb<br>E6 xb ff<br>E6 xb ge ff<br>E6 xb ge ff<br>E6 xb ge ff | P                                                          | 9<br>169<br>169<br>170<br>1879<br>1818                         |      | ΔΔ0- |

| LDD topritii LDD opritii LDD opritii LDD opritii LDD opritii LDD opritiii LDD opritiiii LDD opritiiiii LDD opritiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiii                                       | (M:M+1) → A:B<br>Load Double Accumulator D (A:B)                                | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [IDX2] | CC jj kk DC dd FC hh 11 EC xb EC xb ff EC xb ff EC xb se ff EC xb se ff                      | PO<br>RPE<br>RPO<br>RPE<br>RPO<br>ERPP<br>EIERPE<br>EIERPE | 0F<br>26F<br>26F<br>2F0<br>2F0<br>5ZF7<br>5ZFF<br>5ZFF<br>5ZFF |      | ΔΔ0- |

Note 1. OPPP/OPO indicates this instruction takes four cycles to refill the instruction quaue if the branch is taken and three cycles if the branch is not taken.

Table A-1. Instruction Set Summary (Sheet 3 of 14)

| Source Form                                                   | Operation                                                                                                                                | Addr.<br>Mode     | Machine<br>Coding (box)             | Access Deta              | MESHC12                  | SXHI | NZVC |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------|--------------------------|--------------------------|------|------|

| DIO - h                                                       | Proch 21 con a Con-                                                                                                                      | REL               | Coding (hex)                        | HCS12                    |                          |      |      |

| BLS als                                                       | Branch if Lower or Same<br>(if C + Z = 1) (unsigned)                                                                                     | HEL               | 23 rr                               | PPP/P1                   | PPP/P*                   |      |      |

| BLT ral8                                                      | Branch if Less Than<br>(if N ⊕ V = 1) (signed)                                                                                           | REL               | 2D rr                               | ppp/pl                   | ppp/pl                   |      |      |

| BMI rub                                                       | Branch if Minus (if N = 1)                                                                                                               | REL               | 2B rr                               | 999/p <sup>1</sup>       | PPP/p <sup>1</sup>       |      |      |

| BNE rol8                                                      | Branch if Not Equal (if Z = 0)                                                                                                           | REL               | 26 rr                               | PPP/p <sup>1</sup>       | ppp/p <sup>1</sup>       |      |      |

| BPL mB                                                        | Branch if Plus (if N = 0)                                                                                                                | REL               | 2A rr                               | ppp/p <sup>1</sup>       | ₽₽₽/₽ <sup>1</sup>       |      |      |

| BRAnelB                                                       | Branch Always (if 1 = 1)                                                                                                                 | REL               | 20 rr                               | 222                      | PPP                      |      |      |

| BROLR oprise, make, rate                                      | Branch if (M) • (mm) = 0<br>(if All Selected Bit(s) Clear)                                                                               | DIR               | 4F dd mm rr<br>1F hh 11 mm rr       | 1979<br>1999             | r999<br>rE999            |      |      |

| BROLR opri6a, msk8, ral8<br>BROLR opri0_xysp, msk8, ral8      | (II All Selected Bit(s) Clear)                                                                                                           | IDX               | OF xb mm rr                         | 1979                     | 1555                     |      |      |

| BROLR oproxyxysp, make, rede                                  |                                                                                                                                          | IDX1              | OF xb ff mm rr                      | rfppp                    | rffppp                   |      |      |

| BRCLR opnx16_xysp, msk8, rul8                                 | D. I. N. G. al.                                                                                                                          | IDX2              | OF xb ee ff mm rr                   | Prippp                   | ErPEEPPP                 |      |      |

| BRN rails                                                     | Branch Never (if 1 = 0)                                                                                                                  | REL               | 21 rr                               | P                        | P                        |      |      |

| BRSET opr8, msk8, ral8<br>BRSET opr18a, msk8, ral8            | Branch if (M) • (mm) = 0                                                                                                                 | DIR               | 4E dd mm rr<br>1E hh 11 mm rr       | 1999<br>1999             | rPFF<br>rEFFF            |      |      |

| BRSET opmo xysp, msk8, ral8                                   | (if All Selected Bit(s) Set)                                                                                                             | IDX               | OR xb mm rr                         | IPPP                     | rPPP                     |      |      |

| BRSET oprotizysp, msk8, rel8<br>BRSET oprotiExysp, msk8, rel8 |                                                                                                                                          | IDX1<br>IDX2      | OR xb ff mm rr<br>OR xb ee ff mm rr | rfppp<br>prfppp          | rffppp<br>frpffppp       |      |      |

| BSET opr8, msk8                                               | $(M) + (mm) \rightarrow M$                                                                                                               | DIR               | 4C dd mn                            | rPw0                     | rPOw                     |      | ΔΔ0- |

| BSET opr16s, msk8                                             | Set Bit(s) in Memory                                                                                                                     | EXT               | 1C hh 11 mm                         | rPeP                     | rFFw                     |      | AAU- |

| BSET opnx0_xysp, msk8                                         | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                  | IDX               | OC xb mm                            | rPw0                     | rPOw                     |      |      |

| BSET opnx0,xysp, msk8<br>BSET opnx16,xysp, msk8               |                                                                                                                                          | IDX1<br>IDX2      | OC xb ff mm<br>OC xb se ff mm       | rPwP<br>frPwPO           | rPwP<br>ErPwOP           |      |      |

| BSR role                                                      | $(SP) - 2 \rightarrow SP$ ; $HTN_H; HTN_L \rightarrow M_SP; M_SP+1$                                                                      | REL               | 07 rr                               | SPPP                     | PPPS                     |      |      |

| barries                                                       | Subroutine address → PC                                                                                                                  | HEL               | 07 11                               |                          | *****                    |      |      |

|                                                               | Branch to Subroutine                                                                                                                     |                   |                                     |                          |                          |      |      |

| BVC reds                                                      | Branch if Overflow Bit Clear (if V = 0)                                                                                                  | REL               | 28 rr                               | ppp/p1                   | PPP/P1                   |      |      |

| BVS ral8                                                      | Branch if Overflow Bit Set (if V = 1)                                                                                                    | REL               | 29 rr                               | 999/p <sup>1</sup>       | PPP/P1                   |      |      |

| CALL opri8a, page<br>CALL opri0_xysp, page                    | $(SP) - 2 \rightarrow SP$ ; $HTN_{LC}HTN_{L} \rightarrow M_{(SP)}M_{(SP+1)}$<br>$(SP) - 1 \rightarrow SP$ ; $(PPG) \rightarrow M_{(SP)}$ | EXT               | 4A hh 11 pg<br>4B xb pg             | gnSePPP<br>gnSePPP       | gnfSaPFF<br>gnfSaPFF     |      |      |

| CALL oprixit xysp, page                                       | pg → PPAGE register; Program address → PC                                                                                                | IDX1              | 4B xb ff pg                         | gnSaPPP                  | gnfSarrr                 |      |      |

| CALL oprort6 xysp, page                                       |                                                                                                                                          | 10002             | 4B xb ee ff pg                      | fgnSaPPP                 | fgnfSæPPP                |      |      |

| CALL [D, xysp]<br>CALL [opox16, xysp]                         | Call subroutine in extended memory<br>(Program may be located on another                                                                 | [D,IDX]<br>[IDX2] | 4B xb ee ff                         | flignSaPPP<br>flignSaPPP | flignSaPPP<br>flignSaPPP |      |      |

| CALL [obs./ of xlob)                                          | expansion memory page.)                                                                                                                  | (itota)           | 40 XD 66 11                         | 111gillarrr              | g.warrr                  |      |      |

|                                                               | Life de la                                                                                           |                   |                                     |                          |                          |      |      |

|                                                               | Indirect modes get program address<br>and new pg value based on pointer.                                                                 |                   |                                     |                          |                          |      |      |

| CBA                                                           | (A) – (B)<br>Compare 8-Bit Accumulators                                                                                                  | INH               | 18 17                               | 00                       | 00                       |      | ΔΔΔΔ |

| CLC                                                           | 0 → C                                                                                                                                    | IMM               | 10 FE                               | P                        | P                        |      | 0    |

|                                                               | Translates to ANDCC #\$FE                                                                                                                |                   |                                     |                          |                          |      |      |

| CLI                                                           | 0 → 1<br>Translates to ANDCC #SEF                                                                                                        | IMM               | 10 RF                               | P                        | P                        | 0    |      |

|                                                               | (anablas I-bit interrupts)                                                                                                               |                   |                                     |                          |                          |      |      |

| CLR opr18a                                                    | 0 → M Clear Memory Location                                                                                                              | EXT               | 79 hh 11                            | PwO                      | WOP                      |      | 0100 |

| CLR opnic_xysp                                                |                                                                                                                                          | IDX               | 69 xb                               | Pw                       | Pw                       |      |      |

| CLR oprasil xysp<br>CLR oprasili xysp                         |                                                                                                                                          | IDX1<br>IDX2      | 69 xb ff<br>69 xb ee ff             | Pw0<br>PwP               | PwP                      |      |      |

| CLR [D,xysp]                                                  |                                                                                                                                          | [D,IDX]           | 69 xb                               | PIfw                     | PIEPW                    |      |      |

| CLR [oprox16,xysp]<br>CLRA                                    | O A Class Assumulation A                                                                                                                 | [IDX2]            | 69 xb se ff                         | PIPw                     | PIPPW                    |      |      |

| CLRB                                                          | 0 → A Clear Accumulator A<br>0 → B Clear Accumulator B                                                                                   | INH               | 87<br>C7                            | 0                        | 0                        |      |      |

| CLV                                                           | 0 → V                                                                                                                                    | IMM               | 10 FD                               | P                        | P                        |      | 0-   |

|                                                               | Translates to ANDCC #\$FD                                                                                                                |                   |                                     |                          |                          |      |      |

Note 1. PPP/P indicates this instruction takes three cycles to refill the instruction queue if the branch is taken and one program fetch cycle if the branch is not taken.

Table A-1. Instruction Set Summary (Sheet 4 of 14)

|                                    |                                                                       | Addr.              | Machine              | Access Detail            |      |                                  |

|------------------------------------|-----------------------------------------------------------------------|--------------------|----------------------|--------------------------|------|----------------------------------|

| Source Form                        | Operation                                                             | Mode               | Coding (hex)         | HCS12 M68HC12            | SXHI | NZVC                             |

| CMPB #apr8i                        | (E) - (M)                                                             | MM                 | C1 11                | P                        | 1    | $\Delta\Delta\Delta\Delta\Delta$ |

| CMPB opr8s                         | Compare Accumulator B with Memory                                     | DIR                | D1 dd<br>F1 hh 11    | r9f rf1                  |      |                                  |

| CMPB opri6a<br>CMPB opri0_xysp     |                                                                       | IDX                | F1 nn 11             | rpf rf:                  |      |                                  |

| CMPB optx0_xysp                    |                                                                       | IDX1               | El xb ff             | r90 r90                  |      |                                  |

| CMPB oprox16,xysp                  |                                                                       | IDX2               | El xb ee ff          | free free                |      |                                  |

| CMPB [D,xysp]                      |                                                                       | [D,IDX]            | El xb                | fifepf fifefi            |      |                                  |

| CMPB [qp/xr16,xysp]                |                                                                       | [IDX2]             | El xb ee ff          | firerf firef:            | ,    | ll                               |

| COM opr18a                         | $(\overline{M}) \rightarrow M$ equivalent to SFF $-(M) \rightarrow M$ | EXT                | 71 hh 11             | r9w0 r099                |      | $\Delta\Delta01$                 |

| COM apmo_xysp                      | 1's Complement Memory Location                                        | IDX                | 61 xb                | 15A 15                   |      |                                  |

| COM oprxii),xysp                   |                                                                       | IDX1<br>IDX2       | 61 xb ff             | rPw0 rP00<br>frPwP frPP0 |      | ll                               |

| COM oproc16,xysp<br>COM [D,xysp]   |                                                                       | ID,IDXI            | 61 xb ee ff<br>61 xb | fifre fifre              | 1    | ll                               |

| COM [oprx16,xysp]                  | CO . A Complement Assessed to A                                       | 1DX21              | 61 xb ee ff          | firePw firePo            |      | ll                               |

| COMA                               | (A) → A Complement Accumulator A                                      | "INH"              | 41                   | 0 0                      |      | ll                               |

| COMB                               | (B) → B Complement Accumulator B                                      | INH                | 51                   | 0 (                      | 0    |                                  |

| CPD #opr16i                        | (A:B) - (M:M+1)                                                       | IMM                | 8C jj kk             | PO DI                    |      | $\Delta\Delta\Delta\Delta\Delta$ |

| CPD opirSa                         | Compare D to Memory (16-Bit)                                          | DIR                | 9C dd                | RPf Rf:                  |      |                                  |

| CPD opr18a                         |                                                                       | EXT                | BC hh 11             | RPO ROS                  | 1    | ll                               |

| CPD aprix0_xysp                    |                                                                       | IDX<br>IDX1        | AC xb<br>AC xb ff    | RPF RF1                  |      | ll                               |

| CPD opnx9,xysp<br>CPD opnx16,xysp  |                                                                       | IDX1               | AC xb se ff          | ERPP ERP                 |      | ll                               |

| CPD [D,xysp]                       |                                                                       | ID,IDXI            | AC xb cc 11          | fifapf fifafi            |      | ll                               |

| CPD [oprx16,xysp]                  |                                                                       | [1002]             | AC xb ee ff          | firer firef              |      |                                  |

| CPS#apr16i                         | (SP) - (M:M+1)                                                        | IMM                | 8F jj kk             | PO O                     |      | $\Delta\Delta\Delta\Delta\Delta$ |

| CPS oprise                         | Compare SP to Memory (16-Bit)                                         | DIR                | 9F dd                | RPf Rf:                  |      |                                  |

| CPS opr16a                         |                                                                       | EXT                | BF hh 11             | RPO RO                   | 1    |                                  |

| CPS oprx0_xysp                     |                                                                       | IDX                | AF xb                | RPE RE                   |      | ll                               |

| CPS oproxysp                       |                                                                       | IDX1<br>IDX2       | AF xb ff             | RPO RPO<br>FRED FRED     |      | ll                               |

| CPS opnx18,xysp<br>CPS [D,xysp]    |                                                                       | ID,IDXI            | AF xb ee ff<br>AF xb | fifRPf fifRf:            | 1    | ll                               |

| CPS [aprx:16,xysp]                 |                                                                       | 100021             | AF xb ee ff          | figge figge              |      | ll                               |

| CPX #aport &i                      | (X) - (M:M+1)                                                         | IMM                | 8E 11 kk             | PO 01                    |      | ΔΔΔΔ                             |

| CPX oprSu                          | Compare X to Memory (16-Bit)                                          | DIR                | 9E dd                | RPE RE                   | ,    |                                  |

| CPX opr16a                         |                                                                       | EXT                | BE hh 11             | RPO ROS                  |      | ll                               |

| CPX opni0_xysp                     |                                                                       | IDX                | AE xb                | RPE RE                   |      | ll                               |

| CPX oprx9,xysp                     |                                                                       | IDX1               | AE xb ff             | RPO RPO                  | 1    | ll                               |

| CPX oprox18,xysp<br>CPX [D,xysp]   |                                                                       | IDX2<br>ID,IDX1    | AE xb ee ff<br>AE xb | free free                |      | ll                               |

| CPX [oprat6,xysp]                  |                                                                       | [DX2]              | AE xb se ff          | figge figge              |      |                                  |

| CPY #apr16i                        | (Y) - (M:M+1)                                                         | IMM                | 8D 11 kk             | PO 01                    | _    | ΔΔΔΔ                             |

| CPY oprSu                          | Compare Y to Memory (16-Bit)                                          | DIR                | 9D dd                | RPf RF                   | 1    | адаа                             |

| CPY opri6a                         |                                                                       | EXT                | BD hh 11             | RPO RO                   |      | ll                               |

| CPY opnio_xysp                     |                                                                       | IDX                | AD xb                | RPf Rf:                  | ,    | ll                               |

| CPY oprx9.xysp                     |                                                                       | IDX1               | AD xb ff             | RPO RPO                  |      | ll                               |

| CPY oprx16 xysp                    |                                                                       | IDX2               | AD xb ee ff          | free free                |      | ll                               |

| CPY [D,xysp]<br>CPY [aprx:16,xysp] |                                                                       | [D,IDX]<br>11DX(21 | AD xb<br>AD xb ee ff | firef firef              | 1    | ll                               |

| DAA                                | Adjust Sum to BCD                                                     | INH                | 18 07                | ofo of                   |      | ΔΔ7Δ                             |

|                                    | Decimal Adjust Accumulator A                                          |                    |                      |                          |      |                                  |

| DBEQ abdays, relit                 | (ontr) – 1→ ontr                                                      | REL                | 04 1b rr             | PFF (branch) FFF         |      |                                  |

|                                    | if (cntr) = 0, then Branch                                            | (9-bit)            |                      | PPO (no                  |      |                                  |

|                                    | else Continue to next instruction                                     |                    |                      | branch)                  |      |                                  |

|                                    | Decrement Counter and Branch if = 0                                   |                    |                      |                          |      |                                  |

|                                    | (ontr = A, B, D, X, Y, or SP)                                         |                    |                      |                          |      |                                  |

| DBNE abdxys, ral9                  | (ontr) - 1 → ontr                                                     | REL                | 04 lb rr             | PPP (branch) PPI         |      |                                  |

|                                    | If (ontr) not = 0, then Branch;                                       | (G-bit)            |                      | PPO (no                  | 1    |                                  |

|                                    | else Continue to next instruction                                     |                    |                      | branch)                  | 1    |                                  |

|                                    | Decrement Counter and Branch if ≠ 0                                   | 1                  |                      | I                        | 1    |                                  |

|                                    | (ontr = A, B, D, X, Y, or SP)                                         |                    |                      |                          |      |                                  |

|                                    |                                                                       | <b>—</b>           | L                    | <b>.</b>                 | -    | -                                |

# **DBNE**

#### Decrement and Branch if Not Equal to Zero

**DBNE**

Operation

$(counter) - 1 \Rightarrow counter$

If (counter) not = 0, then (PC) +  $$0003 + rel \Rightarrow PC$

Subtracts one from the counter register A, B, D, X, Y, or SP. Branches to a relative destination if the counter register does not reach zero. Rel is a 9-bit two's complement offset for branching forward or backward in memory. Branching range is \$100 to \$0FF (-256 to +255) from the address following the last byte of object code in the instruction.

CCR Effects

S X H I N Z V C

Code and CPU Cycles

| Source Form        | Address<br>Mode | Machine<br>Code (Hex) | CPU Cycles                      |  |

|--------------------|-----------------|-----------------------|---------------------------------|--|

| DBNE abdxysp, rei9 | REL<br>(9-bit)  |                       | PPP (branch)<br>PPO (no branch) |  |

| Loop Primitive Postbyte (1ь) Coding |                       |                |                     |          |  |  |  |

|-------------------------------------|-----------------------|----------------|---------------------|----------|--|--|--|

| Source<br>Form                      | Postbyte <sup>1</sup> | Object<br>Code | Counter<br>Register | Offset   |  |  |  |

| DBNE A, rei9                        | 0010 X000             | 04 20 rr       | A                   | Positive |  |  |  |

| DBNE B, rei9                        | 0010 X001             | 04 21 rr       | B                   |          |  |  |  |

| DBNE D, rei9                        | 0010 X100             | 04 24 rr       | D                   |          |  |  |  |

| DBNE X, rei9                        | 0010 X101             | 04 25 rr       | X                   |          |  |  |  |

| DBNE Y, rei9                        | 0010 X101             | 04 26 rr       | Y                   |          |  |  |  |

| DBNE SP, rei9                       | 0010 X110             | 04 27 rr       | SP                  |          |  |  |  |

| DBNE A, rei9                        | 0011 X000             | 04 30 rr       | A                   | Negative |  |  |  |

| DBNE B, rei9                        | 0011 X001             | 04 31 rr       | B                   |          |  |  |  |

| DBNE D, rei9                        | 0011 X100             | 04 34 rr       | D                   |          |  |  |  |

| DBNE X, rei9                        | 0011 X101             | 04 35 rr       | X                   |          |  |  |  |

| DBNE Y, rei9                        | 0011 X110             | 04 36 rr       | Y                   |          |  |  |  |

| DBNE SP, rei9                       | 0011 X111             | 04 37 rr       | SP                  |          |  |  |  |

NOTES:

Bits 7:6:5 select DBEQ or DBNE; bit 4 is the offset sign bit: bit 3 is not used; bits 2:1:0 select

the counter register.

**EE 308**

# MC9S12 Cycles

- MC9S12 works on 48 MHz clock

- A processor cycle takes 2 clock cycles P clock is 24 MHz

- Each processor cycle takes **41.7 ns** (1/24 μs) to execute

- An instruction takes from **1** to **12** processor cycles to execute

- You can determine how many cycles an instruction takes by looking up the CPU cycles for that instruction in the Reference Manual.

- For example, **LDAB** using the **IMM** addressing mode shows one CPU cycle (of type P).

- **LDAB** using the **EXT** addressing mode shows three CPU cycles (of type **rPO**).

- Section 6.6 of the S12CPUV2 Reference Manual explains what the HCS12 is doing during each of the different types of CPU cycles.

| 2000          | org \$2000 | ; Inst  | Mode   | <b>Cycles</b> |

|---------------|------------|---------|--------|---------------|

| 2000 C6 0A    | ldab #10   | ; LDAB  | (IMM)  | 1             |

| 2002 87       | loop:clra  | ; CLRA  | (INH)  | 1             |

| 2003 04 31 FC | dbne b,loo | op; DBN | E (REL | ) 3           |

| 2006 3F       | swi        | ; SWI   |        | 9             |

The program executes the **ldab** #10 instruction once. It then goes through the loop 10 times (which has two instructions, one with one cycle and one with three cycles), and finishes with the swi instruction (which takes 9 cycles).

Total number of cycles:

$$1 + 10 \times (1 + 3) + 9 = 50$$

$$50 \text{ cycles} = 50 \times 41.7 \text{ ns/cycle} = 2.08 \text{ μs}$$

**LDAB**

Load B

**LDAB**

OF

$\mathsf{imm} \Rightarrow \mathsf{B}$

Loads B with either the value in M or an immediate value.

CCR

Effects

| 5 | Х | н |   | N | _ | V | C |

|---|---|---|---|---|---|---|---|

| - | - | - | - | Δ | Δ | 0 | - |

N: Set if MSB of result is set; cleared otherwise

Z: Set if result is \$00; cleared otherwise

V: Cleared

Code and CPU Cycles

| Source Form                                                                                                                                           | Address<br>Mode                          | Machine<br>Code (Hex)                                          | CPU Cycles                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------|--------------------------------------|

| LDAB #opr8i<br>LDAB opr16a<br>LDAB opr16a<br>LDAB oprx0_xysppc<br>LDAB oprx16,xysppc<br>LDAB oprx16,xysppc<br>LDAB [D,xysppc]<br>LDAB [oprx16,xysppc] | IMM DIR EXT IDX IDX1 IDX2 [D,IDX] [IDX2] | C6 ii D6 dd F6 hh l1 E6 xb E6 xb ff E6 xb ee ff E6 xb E6 xb ef | P rPf rPO rPf rPO frPP fIfrPf fIPrPf |

**EE 308**

### **Assembler Directives**

- In order to write an assembly language program it is necessary to use assembler directives.

- T hese are not instructions which the HC12 executes but are directives to the assembler program about such things as where to put code and data into memory.

- CodeWarrior has a large number of assembler directives, which can be found in the CodeWarrior help section.

- We will use only a few of these directives. (Note: In the following table, [] means an optional argument.) Here are the ones we will need:

| Directive | Description                     |        | Example           |

|-----------|---------------------------------|--------|-------------------|

| Name      | Cincolor to a small al          | 1      | 100               |

| equ       | Give a value to a symbol        | len:   | equ 100           |

| org       | Set starting value of location  |        | org \$1000        |

|           | counter where code or data      |        |                   |

|           | will go                         |        |                   |

| dc.b      | Allocate and initialize storage | var:   | dc.b 2,18         |

|           | for 8-bit variables.            | name   | : dc.b "Jane"     |

|           | Place the bytes in successive   |        |                   |

|           | memory locations                |        |                   |

| dc.w      | Allocate and initialize storage | var:   | dc.w \$ABCD       |

|           | for 16-bit variables.           |        |                   |

|           | Place the bytes in successive   |        |                   |

|           | memory locations                |        |                   |

| ds.b      | Allocate specified number of    | Table  | : ds.b 10         |

|           | 8-bit storage places            |        |                   |

|           | 3 1                             |        |                   |

| ds.w      | Allocate specified number of    | table: | ds.w 50           |

|           | 16-bit storage spaces           |        |                   |

|           | _ constant go apares            |        |                   |

| dcb.b     | Fill memory with a given        | init d | lata: dcb.b 100,0 |

|           | value:                          |        |                   |

|           | The first value is the number   |        |                   |

|           | of bytes to fill.               |        |                   |

|           | The second number is the        |        |                   |

|           |                                 |        |                   |

|           | value to put into memory        |        |                   |

# Using labels in assembly programs

A **label** is defined by a name followed by a colon as the first thing on a line. When the label is referred to in the program, it has the numerical value of the location counter when the label was defined.

Here is a code fragment using labels and the assembler directives dc and ds:

org \$2000

table1: dc.b \$23,\$17,\$f2,\$a3,\$56

table2: ds.b 5

var: dc.w \$43af

The CodeWarrior assembler produces a listing file (**.lst**). Here is the listing file from the assembler:

Freescale HC12-Assembler (c) Copyright Freescale 1987-2009

| Abs. | Rel.  | Loc   | Obj. code | Source line |      |                          |

|------|-------|-------|-----------|-------------|------|--------------------------|

|      |       |       |           |             |      |                          |

| 1    | 1     |       |           |             | org  | \$2000                   |

| 2    | 2 a00 | 02000 | 2317 F2A3 | table1:     | dc.b | \$23,\$17,\$f2,\$a3,\$56 |

|      | 00    | 02004 | 56        |             |      |                          |

| 3    | 3 a00 | 02005 |           | table2:     | ds.b | 5                        |

| 4    | 4 a00 | 0200A | 43AF      | var:        | dc.w | \$43af                   |

| 5    | 5     |       |           |             |      |                          |

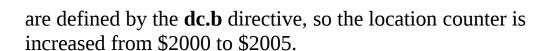

Note that **table1** is a name with the value of \$2000, the value of the location counter defined in the **org** directive. Five bytes of data

Note that **table2** is a name with the value of \$2005. Five bytes of data are set aside for table2 by the **ds.b** 5 directive. The as12 assembler initialized these five bytes of data to all zeros. **var** is a name with the value of \$200a, the first location after table2.

#### **HC12 Instructions**

- 1. Data Transfer and Manipulation Instructions instructions which move and manipulate data (S12CPUV2 Reference Manual, Sections 5.3, 5.4, and 5.5).

- Load and Store load copy of memory contents into a register; store copy of register contents into memory.

LDAA \$2000 ; Copy contents of addr \$2000 into A STD 0,X ; Copy contents of D to addrs X and X+1

• Transfer — copy contents of one register to another.

TBA ; Copy B to A TFR X,Y ; Copy X to Y

• Exhange — exchange contents of two registers.

XGDX ; Exchange contents of D and XEXG A,B ; Exchange contents of A and B

• Move — copy contents of one memory location to another.

MOVB \$2000,\$20A0; Copy byte at \$2000 to \$20A0

MOVW 2,X+,2,Y+ ; Copy two bytes from address held

; in X to address held in Y

; Add 2 to X and Y

2. Arithmetic Instructions — addition, subtraction, multiplication, division (**S12CPUV2 Reference Manual**, Sections 5.6, 5.8 and 5.12).

ABA ; Add B to A; results in A

SUBD \$20A1 ; Subtract contents of \$20A1 from D

INX ; Increment X by 1

MUL ; Multiply A by B; results in D

- 3. Logic and Bit Instructions perform logical operations (**S12CPUV2 Reference Manual**, Sections 5.9, 5.10, 5.11, 5.13 and 5.14).

- Logic Instructions

ANDA \$2000 ; Logical AND of A with contents of

; \$2000

EORB 2,X ; Exclusive OR B with contents of

; address (X+2)

• Clear, Complement and Negate Instructions

NEG -2,X; Negate (2's comp) contents of

; address (X-2)

CLRA ; Clear ACC A

• Bit manipulate and test instructions — work with bits of a register or memory.

BITA #\$08 ; Check to see if Bit 3 of A is set BSET \$0002,#\$18 ; Set bits 3 and 4 of address \$0002

• Shift and rotate instructions

LSLA ; Logical shift left A

ASR \$1000 ; Arithmetic shift right value at address

; \$1000

4. Compare and test instructions — test contents of a register or memory (to see if zero, negative, etc.), or compare contents of a register to memory (to see if bigger than, etc.) (**S12CPUV2 Reference Manual**, Section 5.9).

TSTA ; (A)-0 -- set flags accordingly

CPX #\$8000 ; (X) - \$8000 -- set flags accordingly

5. Jump and Branch Instructions — Change flow of program (e.g., goto, if-then-else, switch-case) (**S12CPUV2 Reference Manual**, Sections 5.19, 5.20 and 5.21).

JMP L1 ; Start executing code at address label

; L1

BEQ L2 ; If Z bit set, go to label L2

DBNE X,L3 ; Decrement X; if X not 0 then goto L3 BRCLR \$1A,#\$80,L4 ; If bit 7 of addr \$1A clear, go to

; label L4

JSR sub1 ; Jump to subroutine sub1 RTS ; Return from subroutine

- 6. Interrupt Instructions Initiate or terminate an interrupt call (**S12CPUV2 Reference Manual**, Section 5.22).

- Interrupt instructions

SWI; Initiate software interrupt RTI; Return from interrupt

7. Index Manipulation Instructions — Put address into X, Y or SP, manipulate X, Y or SP (**S12CPUV2 Reference Manual**, Section 5.23).

ABX ; Add (B) to (X)

LEAX 5,Y ; Put address (Y) + 5 into X

8. Condition Code Instructions — change bits in Condition Code Register (**S12CPUV2 Reference Manual**, Section 5.26).

ANDCC #\$f0 ; Clear N, Z, C and V bits of CCR

SEV ; Set V bit of CCR

9. Stacking Instructions — push data onto and pull data off of stack (**S12CPUV2 Reference Manual**, Section 5.24).

PSHA ; Push contents of A onto stack

PULX ; Pull two top bytes of stack, put into X

10. Stop and Wait Instructions — put MC9S12 into low power mode (S12CPUV2 Reference Manual, Section 5.27).

STOP ; Put into lowest power mode

WAI ; Put into low power mode until next interrupt

11. Null Instructions

NOP ; No operation BRN ; Branch never

**EE 308**

12. Instructions we won't discuss or use — BCD arithmetic, fuzzy logic, minimum and maximum, multiply-accumulate, table interpolation (S12CPUV2 Reference Manual, Sections 5.7, 5.16, 5.17, and 5.18).

# Disassembly of an HC12 Program

• It is sometimes useful to be able to convert *HC12 op codes* into mnemonics.

### For example, consider the hex code:

| ADDR DATA     |      |  |

|---------------|------|--|

| 1000 C6 05 CE | <br> |  |

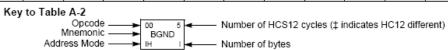

- To determine the instructions, use Table A-2 of the HCS12 Core Users Guide.

- If the first byte of the instruction is anything other than \$18, use Sheet 1 of Table A.2. From this table, determine the number of bytes of the instruction and the addressing mode. For example, **\$C6** is a two-byte instruction, the mnemonic is **LDAB**, and it uses the **IMM** addressing mode. Thus, the two bytes **C6 05** is the op code for the instruction **LDAB #\$05**.

- If the first byte is \$18, use Sheet 2 of Table A.2, and do the same thing. For example, 18 06 is a two byte instruction, the mnemonic is **ABA**, and it uses the **INH** addressing mode, so

there is no operand. Thus, the two bytes **18 06** is the op code for the instruction **ABA**.

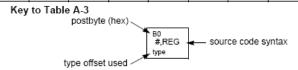

- Indexed addressing mode is fairly complicated to disassemble. You need to use Table A.3 to determine the operand. For example, the op code \$E6 indicates LDAB indexed, and may use two to four bytes (one to three bytes in addition to the op code). The postbyte 01 indicates that the operand is 0,1, which is 5-bit constant offset, which takes only one additional byte. All 5-bit constant offset, pre and post increment and decrement, and register offset instructions use one additional byte. All 9-bit constant offset instructions use two additional bytes, with the second byte holding 8 bits of the 9 bit offset. (The 9th bit is a direction bit, which is held in the first postbyte.) All 16-bit constant offset instructions use three postbytes, with the 2nd and 3rd holding the 16-bit unsigned offset.

- Transfer (**TFR**) and exchange (**EXG**) instructions all have the op code **\$B7**. Use Table A.5 to determine whether it is **TFR** or an **EXG**, and to determine which registers are being used. If the most significant bit of the postbyte is **0**, the instruction is a transfer instruction.

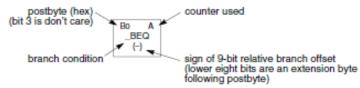

- Loop instructions (Decrement and Branch, Increment and Branch, and Test and Branch) all have the op code **\$04**. To determine which instruction the op code **\$04** implies, and whether the branch is <u>positive</u> (forward) or <u>negative</u> (backward), use Table A.6. For example, in the sequence **04 35 EE**, the 04 indicates a loop instruction. The 35 indicates it is a **DBNE X** instruction (decrement register X and branch if

result is not equal to zero), and the direction is backward (negative). The **EE** indicates a branch of -18 bytes.

\_

• Use up all the bytes for one instruction, then go on to the next instruction.

C6 05  $\Rightarrow$  LDAB #\$05 two-byte LDAB, IMM addressing mode

CE 20 00  $\Rightarrow$  LDX #\$2000 three-byte LDX, IMM addressing mode

E6 01  $\Rightarrow$  LDAB 1,X two to four-byte LDAB,

IDX addressing mode. Operand 01 => 1,X, a 5b constant offset which uses only one postbyte

18 06  $\Rightarrow$  ABA two-byte ABA, INH addressing mode

**04 35 EE** ⇒ **DBNE X,(-18)** three-byte loop instruction Postbyte 35 indicates DBNE X, negative **3F** ⇒ **SWI** one-byte SWI, INH addressing

mode

#### Table A-2. CPU12 Opcode Map (Sheet 1 of 2)

| 00 †5<br>BGND  | ANDCC          | BRA 3          | PULX         | 40 1<br>NEGA | 50 1<br>NEGB | 60 3-6<br>NEG     | 70 4<br>  NEG | SUBA 1       | 90 3<br>SUBA | A0 3-6<br>SUBA | B0 3<br>SUBA | C0 1<br>SUBB | D0 3<br>SUBB | E0 3-6<br>SUBB | F0 3<br>SUBB |

|----------------|----------------|----------------|--------------|--------------|--------------|-------------------|---------------|--------------|--------------|----------------|--------------|--------------|--------------|----------------|--------------|

| IH 1           | IM 2           | RL 2           | IH 1         | IH 1         |              | ID 2-4            | EX 3          |              |              | ID 2-4         |              |              | DI 2         |                |              |

| 01 5           |                | 21 1           | 31 3         | 41 1         | 51 1         | 61 3-6            | 71 4          |              | 91 3         |                | B1 3         |              | D1 3         | E1 3-6         | F1 3         |

| MEM            | EDIV           | BRN            | PULY         | COMA         | COMB         | COM               | COM           | CMPA         | CMPA         | CMPA           | CMPA         | CMPB         | CMPB         | CMPB           | CMPB         |

| IH 1           | IH 1           | RL 2           | IH 1         |              |              |                   | EX 3          |              |              |                |              |              | DI 2         |                | EX 3         |

| 02 1           | 12 ‡1          |                |              | 42 1         |              | 62 3-6            |               |              | 92 3         |                |              |              | D2 3         |                | F2 3         |

| INY 1          | MUL<br>IH 1    | RL 2           | PULA<br>IH 1 | INCA<br>IH 1 | INCB         | INC<br>ID 2-4     | INC<br>EX 3   | SBCA<br>IM 2 | SBCA<br>DI 2 | SBCA<br>ID 2-4 | SBCA<br>EX 3 | SBCB<br>IM 2 | SBCB<br>DI 2 | SBCB<br>ID 2-4 | SBCB<br>EX 3 |

| 02 1           | 13 3           | 23 3/1         |              |              | 53 1         | 63 3-6            |               |              |              |                | B3 3         | C3 2         | D3 3         | E3 3-6         | F3 3         |

| DEY '          | EMUL           | BLS            | PULB         | DECA         | DECB         | DEC               | DEC           | SUBD         | SUBD         | SUBD           | SUBD         | ADDD 2       | ADDD         | ADDD           | ADDD         |

| IH 1           | IH 1           | RL 2           | IH 1         | IH 1         | IH 1         | ID 2-4            | EX 3          | IM 3         | DI 2         | ID 2-4         | EX 3         | IM 3         | DI 2         | ID 2-4         | EX 3         |

| 04 , 3         | 14 1           | 24 3/1         |              |              |              | 64 3-6            |               |              |              | A4 3-6         |              | C4 1         | D4 3         | E4 3-6         | F4 3         |

| loop           | ORCC           | BCC            | PSHX         | LSRA         | LSRB         | LSR               | LSR           | ANDA         | ANDA         | ANDA           | ANDA         | ANDB         | ANDB         | ANDB           | ANDB         |

| RL 3           |                | RL 2           | IH 1         |              |              |                   | EX 3          |              |              |                |              | IM 2         | DI 2         |                | EX 3         |

| JMP            | 15 4-7<br>JSR  | 25 3/1<br>BCS  | 35 2<br>PSHY | 45 1<br>ROLA | 55 1<br>ROLB | 65 3-6<br>ROL     | 75 4<br>ROL   | 85 1<br>BITA | 95 3<br>BITA | A5 3-6<br>BITA | B5 3<br>BITA | C5 1<br>BITB | D5 3<br>BITB | E5 3-6<br>BITB | F5 3<br>BITB |

| ID 2-4         |                | RL 2           |              |              |              | ID 2-4            |               |              |              | ID 2-4         |              | IM 2         |              | ID 2-4         |              |

|                | 16 4           |                |              |              |              | 66 3-6            | 78 4          |              |              | A6 3-6         |              | C6 1         |              |                | F6 3         |

| JMP            | JSR            | BNE            | PSHA         | RORA         | RORB         | ROR               | ROR           | LDAA         | LDAA         | LDAA           | LDAA         | LDAB         | LDAB         | LDAB           | LDAB         |

| EX 3           |                | RL 2           |              |              | IH 1         | ID 2-4            | EX 3          | IM 2         |              | ID 2-4         |              | IM 2         | DI 2         | ID 2-4         | EX 3         |

|                |                | 27 3/1         |              |              |              | 67 3-6            | 77 4          | 1            |              | A7 1           | B7 1         | C7 1         | D7 1         | E7 3-6         | F73          |

| BSR            | JSR            | BEQ            | PSHB         | ASRA         | ASRB         | ASR               | ASR           | CLRA         | TSTA         | NOP            | TFR/EXG      | CLRB         | TSTB         | TST            | TST          |

| RL 2           | DI 2           | RL 2<br>28 3/1 |              |              |              | ID 2-4<br>68 3-6  | EX 3          |              | IH 1<br>98 3 |                | IH 2<br>B8 3 | IH 1         | IH 1         |                |              |

| INX 1          | 18 -<br>Page 2 | BVC 3/1        | 38 3<br>PULC | ASLA         | ASLB         | 08 3-0<br>ASL     | ASL 4         | 88 1<br>EORA | EORA         | A8 3-6<br>EORA | EORA         | C8 1<br>EORB | D8 3<br>EORB | E8 3-6<br>EORB | F8 3<br>EORB |

| IH 1           | - age 2        | RL 2           |              |              |              |                   | EX 3          |              |              |                |              |              |              | ID 2-4         | EX 3         |

| 09 1           | 19 2           | 29 3/1         |              |              |              | 69 ‡2-4           |               | 89 1         |              | A9 3-6         |              | C9 1         | D9 3         | E9 3-6         | F9 3         |

| DEX            | LEAY           | B∀S            | PSHC         | LSRD         | ASLD         | CLR               | CLR           | ADCA         | ADCA         | ADCA           | ADCA         | ADCB         | ADCB         | ADCB           | ADCB         |

| IH 1           |                |                |              |              |              |                   | EX 3          |              |              |                |              |              |              | ID 2-4         |              |

| 0A ±7          | 1A 2<br>LEAX   | 2A 3/1<br>BPL  | 3A 3<br>PULD |              | 5A 2<br>STAA | 6A ‡2-4<br>STAA   | 7A 3<br>STAA  | ORAA 1       | 9A 3<br>ORAA | AA 3-6<br>ORAA | BA 3<br>ORAA | CA 1<br>ORAB | DA 3         |                | FA 3<br>ORAB |

| KIC 1          |                | RL 2           |              | CALL<br>EX 4 |              |                   | EX 3          |              |              |                | EX 3         |              | ORAB<br>DI 2 | ORAB           | EX 3         |

| 0B +8          |                | 2B 3/1         |              |              |              | ID 2-4<br>6B ‡2-4 |               |              |              | AB 3-6         |              |              | DB 3         | EB 3-6         | FB 3         |

| RTI            | LEAS           | BMI            | PSHD         | CALL         | STAB         | STAB              | STAB          | ADDA         | ADDA         | ADDA           | ADDA         | ADDB         | ADDB         | ADDB           | ADDB         |

| IH 1           | ID 2-4         | RL 2           |              | ID 2-5       | DI 2         | ID 2-4            |               | IM 2         |              |                | EX 3         | IM 2         | DI 2         | ID 2-4         | EX 3         |

| OC 4-6         | 1C 4           | 2C 3/1         | +            |              |              | 6C ‡2-4           | 7C 3          |              |              |                |              |              | DC 3         |                | FC 3         |

| BSET           | BSET           | BGE            | wavr         | BSET         | STD          | STD               | STD           | CPD          | CPD          | CPD            | CPD          | LDD          | LDD          | LDD            | LDD          |

| ID 3-5         | EX 4           | RL 2           |              |              |              | ID 2-4            | EX 3          |              |              |                |              |              |              | ID 2-4         |              |

| 0D 4-8<br>BCLR | 1D 4<br>BCLR   | 2D 3/1<br>BLT  | 3D 5<br>RTS  | 4D 4<br>BCLR | 5D 2<br>STY  | 6D ‡2-4<br>STY    | STY 3         | 8D 2<br>CPY  | 9D 3<br>CPY  | AD 3-6<br>CPY  | BD 3<br>CPY  | CD 2<br>LDY  | DD 3         | ED 3-6<br>LDY  | FD 3<br>LDY  |

| ID 3-5         | EX 4           | RL 2           |              | DI 3         |              |                   |               | IM 3         | ı            |                |              |              |              | ID 2-4         |              |

| 0E ±4-6        | 1E 5           |                | 3E ‡†7       |              |              | 6E ±2-4           |               | 8E 2         |              | AE 3-6         |              |              |              |                |              |

| BRSET          | BRSET          | BGT            | WAI          | BRSET        | STX          | STX               | STX           | CPX          | CPX          | CPX            | CPX          | LDX          | LDX          | LDX            | LDX          |

| ID 4-6         | EX 5           |                | IH 1         | DI 4         |              |                   |               |              |              | ID 2-4         |              |              |              | ID 2-4         |              |

| OF ‡4-6        |                | 2F 3/1         |              |              |              | 6F ‡2-4           |               |              |              |                |              |              |              |                | FF 3         |

| BRCLR          | BRCLR          | BLE            | SWI          | BRCLR        | STS          | STS               | STS           | CPS          | CPS          | CPS            | CPS          | LDS          | LDS          | LDS            | LDS          |

| IID 4-61       | EX 5           | RL 2           | IH 1         | DI 4         | DI 2         | ID 2-4            | EX 3          | IM 3         | DI 2         | ID 2-4         | EX 3         | IM 3         | DI 2         | ID 2-4         | EX 3         |

#### Table A-2. CPU12 Opcode Map (Sheet 2 of 2)

| 100 (        | 40 40             |                |                   | 40 40         |               |               | 70 40         | 22 42         |               | 10 10         | DD 40         | 00 40         | 50 40         | == 40         | <b>50</b> 40  |

|--------------|-------------------|----------------|-------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| MOVW 4       | 10 12<br>IDIV     | LBRA           | 30 10<br>TRAP     | 40 10<br>TRAP | 50 10<br>TRAP | 60 10<br>TRAP | 70 10<br>TRAP | 80 10<br>TRAP | 90 10<br>TRAP | A0 10         | B0 10         | C0 10         | D0 10         | TRAP          | TRAP          |

| IM-ID 5      | IH 2              | RL 4           | IH 2              | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          |

| 01 5<br>MOVW | 11 12<br>FDIV     | 21 3<br>LBRN   | 31 10<br>TRAP     | 41 10<br>TRAP | 51 10<br>TRAP | 61 10<br>TRAP | 71 10<br>TRAP | 81 10<br>TRAP | 91 10<br>TRAP | A1 10<br>TRAP | B1 10<br>TRAP | C1 10<br>TRAP | D1 10<br>TRAP | E1 10<br>TRAP | F1 10<br>TRAP |

| EX-ID 5      | IH 2              |                | IH 2              | IH 2          | III 2         | III 2         | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          |

| 02 5         | 12 13             |                | 32 10             |               |               | 62 10         | 72 10         |               |               | A2 10         |               | C2 10         | D2 10         |               | F2 10         |

| ID-ID 4      | EMACS<br>SP 4     | LBHI<br>RL 4   | TRAP              | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          |

| ID-ID 4      | 13 3              | 23 4/3         | IH 2              | IH 2          | IH 2<br>53 10 | IH 2<br>63 10 | IH 2<br>73 10 |               | IH 2<br>93 10 | IH 2<br>A3 10 | IH 2<br>B3 10 |               |               | IH 2<br>E3 10 | IH 2<br>F3 10 |

| MOVW         | EMULS             | LBLS           | TRAP              | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          |

| IM-EX 6      | IH 2              |                | IH 2              | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          | IH 2          |

| 04 6<br>MOVW | 14 12<br>EDIVS    | 24 4/3<br>LBCC | 34 10<br>TRAP     | 44 10<br>TRAP | 54 10<br>TRAP | 64 10<br>TRAP | 74 10<br>TRAP | 84 10<br>TRAP | 94 10<br>TRAP | A4 10<br>TRAP | B4 10<br>TRAP | C4 10<br>TRAP | D4 10<br>TRAP | E4 10<br>TRAP | F4 10<br>TRAP |

| EX-EX 6      |                   | RL 4           | IH 2              |               | IH 2          | IH 2          |               |               |               | IH 2          | IH 2          |               | IH 2          | IH 2          | IH 2          |

| 05 5         | 15 12             | 25 4/3         |                   |               | 55 10         | 65 10         | 75 10         | 85 10         |               | A5 10         |               |               | D5 10         |               | F5 10         |

| MOVW         | IDIVS             | LBCS           | TRAP              | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          | TRAP          |

| ID-EX 5      | IH 2              |                | IH 2              |               | IH 2          | IH 2          | IH 2          | IH 2          |               | IH 2          |