## Lab 9 Introduction to Logic Gates

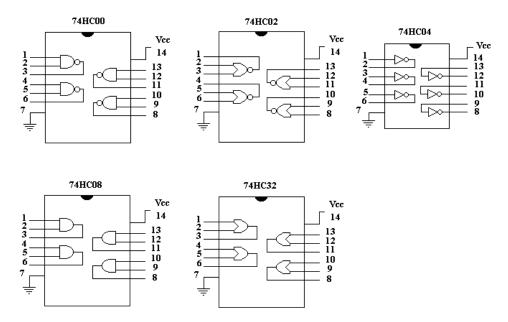

The pinout schemes for the logic gates you will be using in this exercise are given in Figure 1. Note that for all of these chips, Vcc = 5V (pin 14) and GND = 0V (pin 7). Also, note that the pins that are inputs on some chips are not necessarily the inputs on other chips!

Figure 1: 7400 Series

## Prelab

Given the following boolean equation:

$$F = ABCD + \bar{A}BC + A\bar{B}C + \bar{A}\bar{B}CD \tag{1}$$

1. Draw and fully label a schematic using only 04's (NOT's), 08's (AND's), and 32's (OR's).

- 2. Construct a truth table based on this Boolean equation.

- 3. Using a KMAP, derive the minimum equation for the original formula.

- 4. Draw and fully label a schematic from the reduced equation using only 04's, 08's, and 32's.

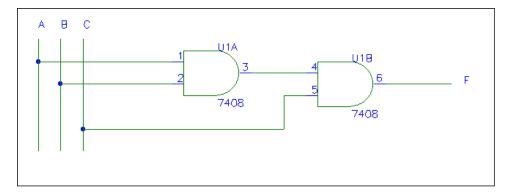

- 5. The following exercises deal with the schematic in Figure 2.

Figure 2: A logic circuit

- (a) From the schematic, derive the Boolean equation for the output, F.

- (b) Write out a truth table based on the equation you derived in the previous part.

## Lab Exercises

- 1. Before using the components shown in Figure 1, it is helpful to understand and observe exactly what we mean when we talk about HI and LO signals, 0 and 1, Vcc and GND, +5 and 0, in logic circuits.

- (a) Connect the 7404, 7408 and 7432 components on your breadboard to Vcc (pin 14) and GND (pin 7). This is the power they need to operate and is independent of any logic circuitry you create.

- (b) Using connections to Vcc (for HI) and GND (for LO) as the A and B inputs to the logic chips, you will implement all the possible input combinations on each type of gate and record the observed values. Remember that a LO means 0v which is a connection to GND. LO is not the same as no connection. If you do not connect the inputs to either Vcc or GND, your IC may behave unpredictably.

- i. Using a multimeter, measure the output voltage (with respect to ground) of each gate for each input combination and record the measured values in the V columns of the truth tables.

- ii. Using a logic probe, determine the logic level output (0 or 1) of each gate type for each input combination and record the measured values in the F columns of the truth tables.

| 74HC04 (NOT gate) | 74HC08 (AND gate) | 74HC32 (OR gate) |  |  |  |  |  |  |

|-------------------|-------------------|------------------|--|--|--|--|--|--|

|                   |                   |                  |  |  |  |  |  |  |

| $A \mid V \mid F$ | 0 0               | 0 0              |  |  |  |  |  |  |

| 0                 | 0 1               | 0 1              |  |  |  |  |  |  |

| 1                 | 1 0               | 1 0              |  |  |  |  |  |  |

|                   | 1   1             |                  |  |  |  |  |  |  |

- 2. Construct the circuit in Figure 2. (Remember to hookup Vcc and ground.) Using a logic probe, observe the values of the output for every possible combination of input. Construct a truth table with your results. The truth table you derived in the prelab should have agreed with the truth table you observed in the previous part. If your two truth tables did not agree, list any problems you found and what you did to correct them.

- 3. Build the minimized version of this circuit which you reduced in the prelab for Equation 1. For every high and low combination of the inputs, test your circuit using a logic probe. The protoboard has some logic level switches you can use to easily switch your inputs. Make sure the row of switches is set to +5 (not +V), connect each input to a switch port and use the switch to select a HI or LO input. Construct a truth table showing your results. Does it match with what you computed in the prelab?

| Don't | ${\it disassemble}$ | your | ${\rm circuit}$ | until | you | have | ${\bf demonstrated}$ | $_{\rm that}$ | it | works | to | a | TA. | TA | INITIALS |

|-------|---------------------|------|-----------------|-------|-----|------|----------------------|---------------|----|-------|----|---|-----|----|----------|

| HEBE  | ١                   |      |                 |       |     |      |                      |               |    |       |    |   |     |    |          |