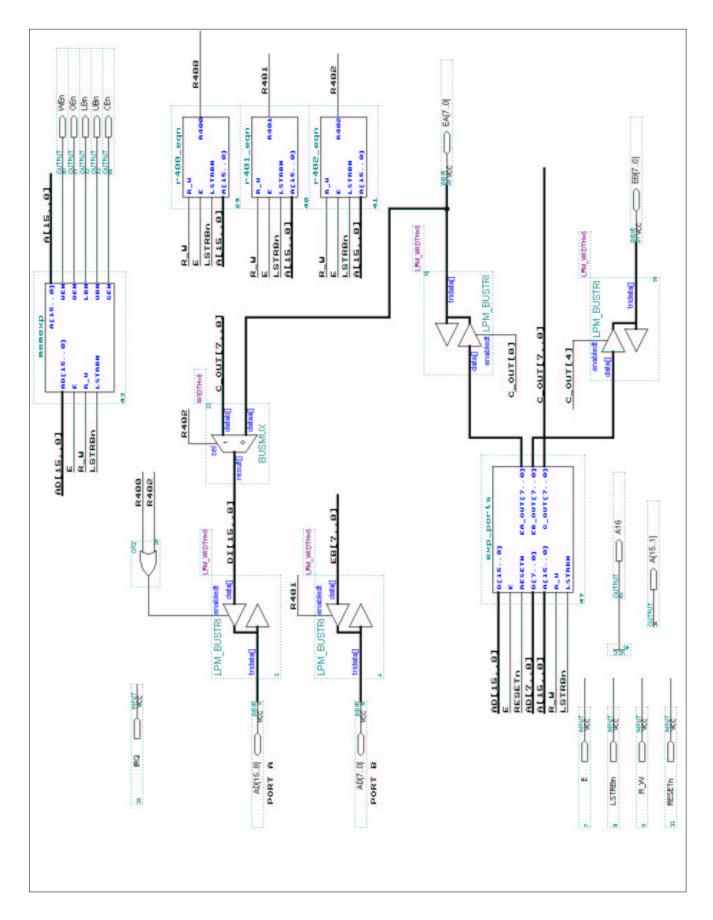

- We will build two bi-directions expansion ports in the Altera EPF7128 chip on the memory expansion board

- The following Altera GDF files show how this is done

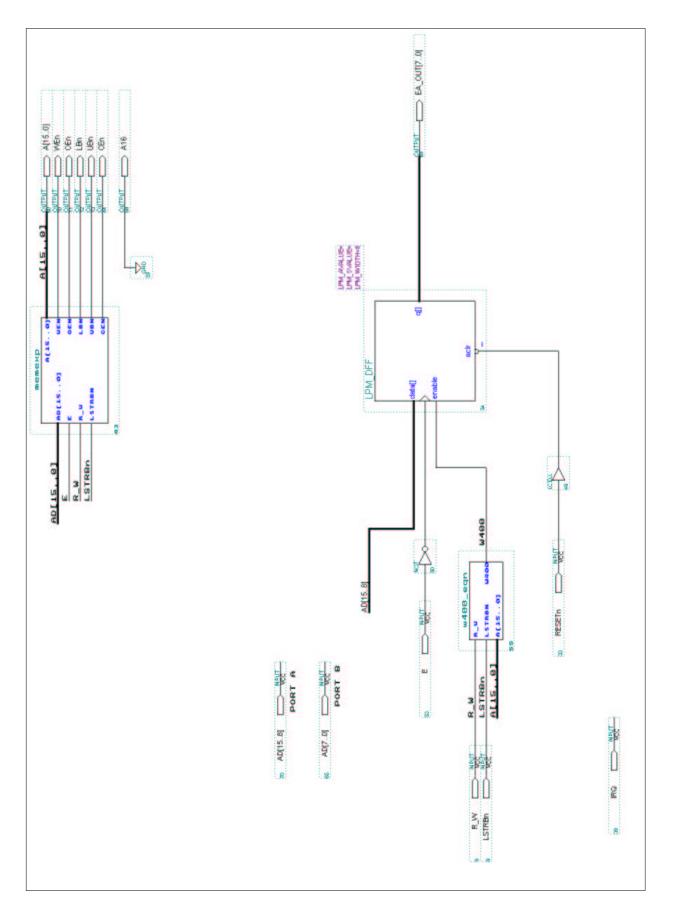

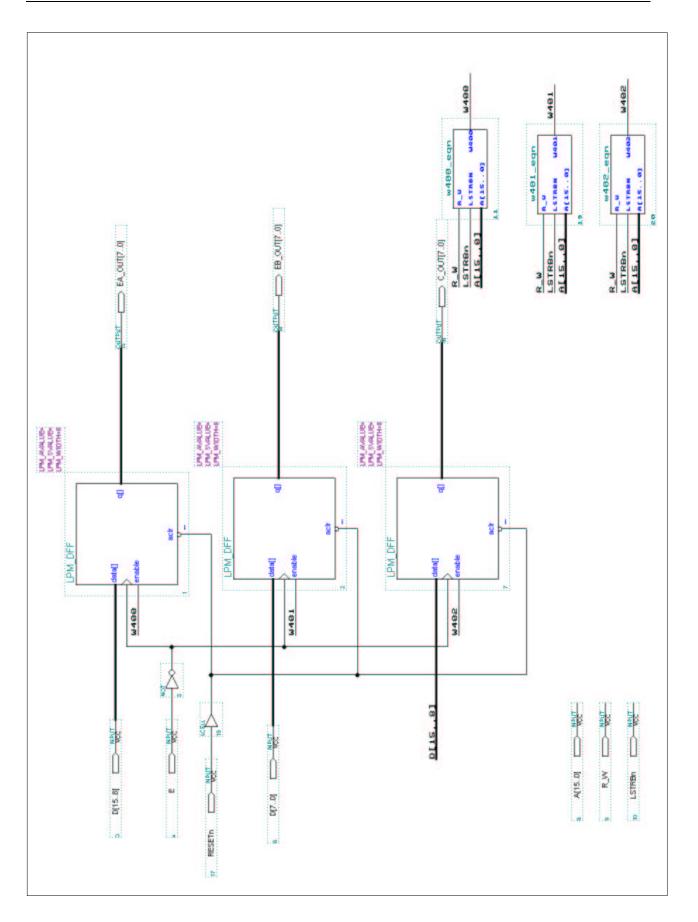

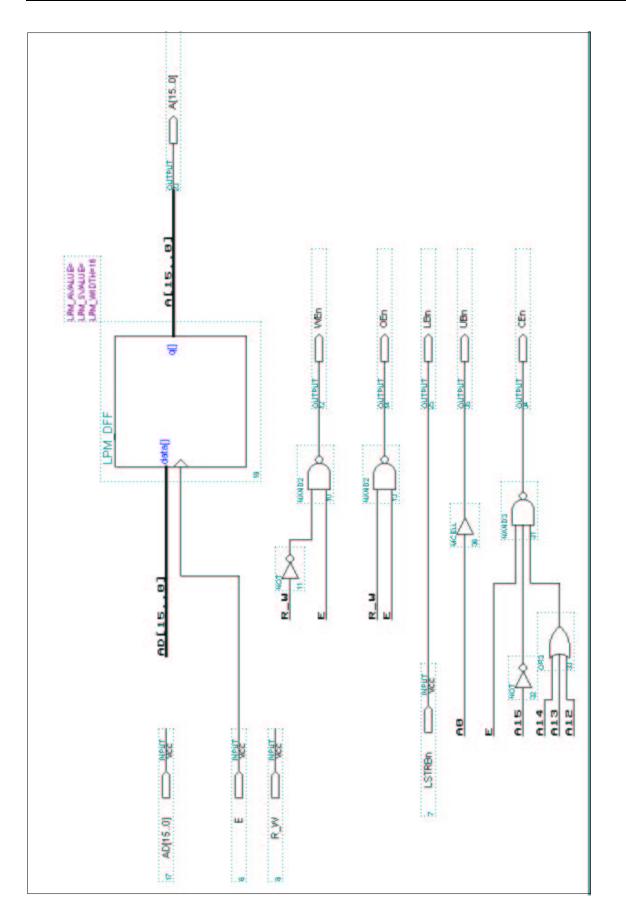

- The first GDF file shows an output port.

- The address is demultiplexed from AD[15..0] in the memexp block

- The output value is latched into the set of 8 flip-flops on a write to address 0x0400

- The D inputs of the flip-flops are connected to AD[15..8], the high (even) byte of the data bus

- The data is latched on the rising edge of E

- The flip-flop latches are enabled on a write to address 0x0400

- Here is the Altera TDF file for determining when a write to address 0x0400 takes place:

```

SUBDESIGN w400_eqn

(

R_W

:

INPUT;

% R/W Line %

LSTRBn

:

INPUT;

A[15..0]

% Demultiplexed address bits %

:

INPUT;

w400

:

OUTPUT;

)

```

```

BEGIN

```

```

if ((A[15..0] == H"0400") & (R_W == GND)) THEN

w400 = VCC;

ELSE

w400 = GND;

END IF;

```

END;

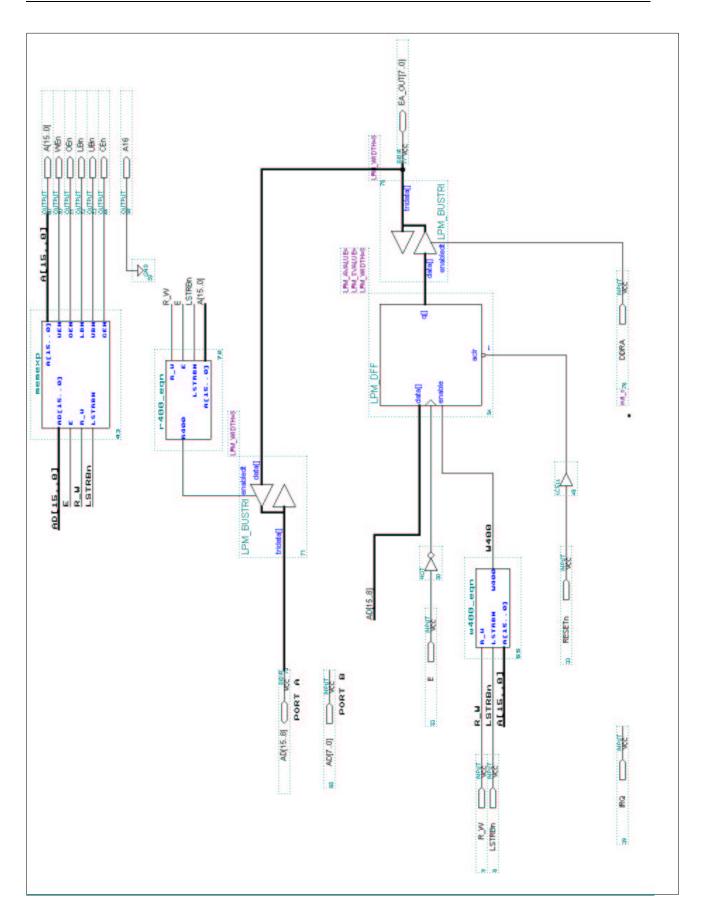

- We now need to be able to read what was written to the expansion port

- We do this by putting a tri-state buffer between the ouput of the expansion port an the address/data bus

- We enable the tri-state buffer on a read from address 0x0400

- Here is the Altera TDF file which determines when we read from address 0x0400:

```

SUBDESIGN r400_eqn

```

| R_W<br>E<br>LSTRBn | : INPUT; % R/W Line %<br>: INPUT;<br>: INPUT; |

|--------------------|-----------------------------------------------|

| A[150]             | : INPUT; % Demultiplexed address bits %       |

| r400<br>)          | : OUTPUT;                                     |

BEGIN

(

if ((A[15..0] == H"0400") & (R\_W == VCC) & (E == VCC)) THEN

r400 = VCC;

ELSE

r400 = GND;

END IF;

END;

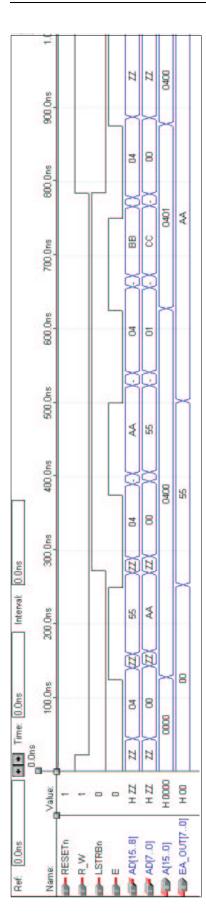

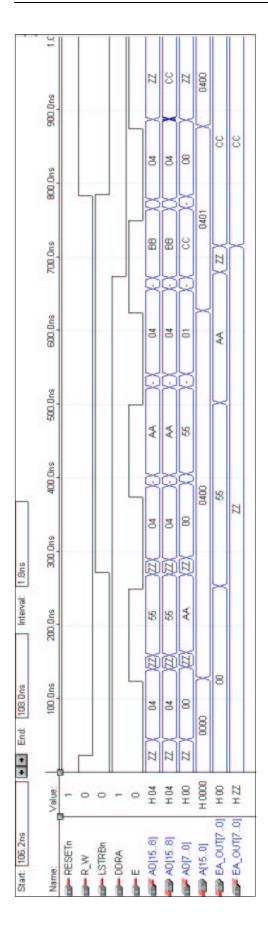

| Start: 267.3ns |        | • • End: 270.0ns | End: | 270.0ns |        | Interval: 2.7ns | 2.7ns   |    |         |         |    |         |    |         |         |    |            |

|----------------|--------|------------------|------|---------|--------|-----------------|---------|----|---------|---------|----|---------|----|---------|---------|----|------------|

| Name:          | Value: | _                |      | 100.0ns | 3      | 200,0ns         | 300.0ns |    | 400.0ns | 500.0ns | su | 600.0ns | 02 | 700,0ns | 800.0ns | 2  | 900.0ns    |

| RESETIN        | -      |                  |      |         |        |                 |         |    |         |         |    |         |    |         |         |    |            |

| R_W            | •      |                  |      |         |        |                 |         |    |         |         |    |         |    |         | L       |    |            |

| LSTRBn         | •      | 2                |      |         |        |                 | 20      | 23 |         |         |    | 3       |    |         |         | 3  |            |

| -              | •      |                  |      |         |        |                 |         |    |         | Γ       |    | -       |    |         |         |    |            |

| AD[158]        | H 66   | Ħ                | L    | 8       |        | 58              |         | 04 |         | AA      |    | 64      | R  | 88      |         | 04 | Z X        |

| AD[15.8]       | H 66   | Ħ                | U    | 8       |        | 8               |         | 04 |         | AA      | R  | 8       |    | 88      |         | 04 | X AA       |

| [0]. 7[dA 🐂    | HAA    | Ħ                |      | 8       | E<br>E | AA              | )(Ħ)    | 8  |         | 8       |    | 6       |    | 23      |         | 8  | Д <u>д</u> |

| A[150]         | H 0400 |                  | 8    | Ñ       |        |                 |         | 40 | 0400    |         |    | Π       |    | 0401    | 5       |    | 0400       |

| EA_OUT70]      | H 66   |                  |      | 8       |        |                 |         | ŝ  | 33      | Ñ       |    |         |    | ¥.      | 4       |    |            |

|                |        |                  |      |         |        |                 |         |    |         |         |    |         |    |         |         |    |            |

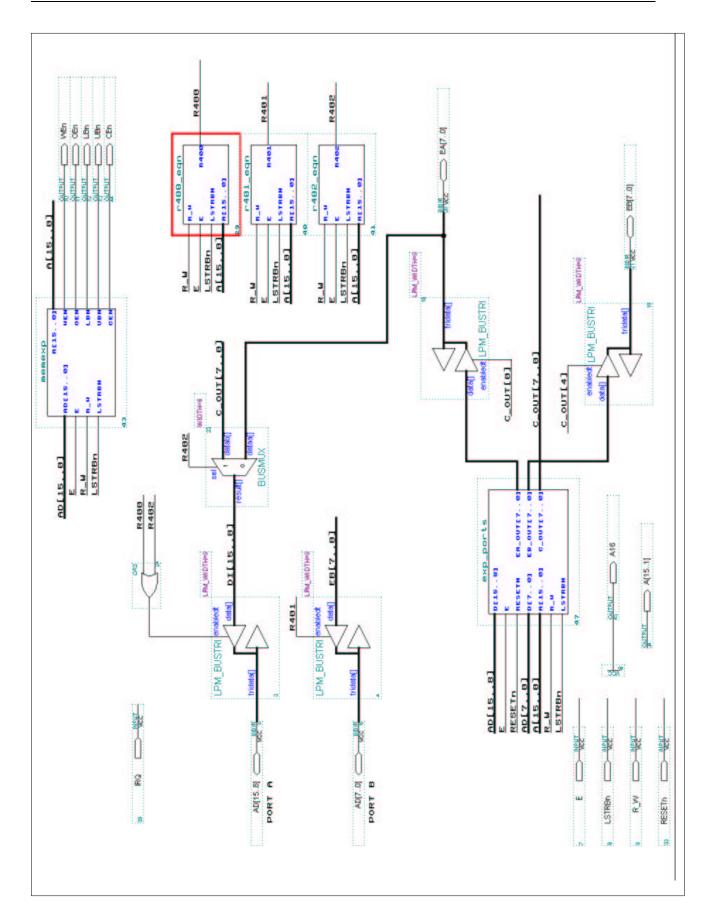

- We now need to make the expansion ports bi-directional

- We do this by putting a tri-state buffer between the output of the flip-flops and the expansion port pins

- We use a data direction input to allow us to choose whether to use the port as an input or output

- If the data direction bit is high, the outputs of the flip-flops are driven onto the expansion port pins, and the port is output

- If the data direction bit is low, the outputs of the flip-flops are not driven onto the expansion port pins, and the port is input

- The data direction bit is a bit of another register built into the Altera chip

- We now add a second bi-directional expansion port at address 0x0401

- The data for this expansion port is connected to AD[7..0], the low data byte

- We also add a register at address 0x0402 to supply the data direction bits for the two new expansion ports

- Bit 0 of address 0x0402 controls the direction of Expansion Port A (EXPA) at address 0x0400

- Bit 4 of address 0x0402 controls the direction of Expansion Port B (EXPB) at address 0x0401

## Using MSI Logic To Build An Output Port

- Many designs use standard MSI logic for microprocessor expansion

- This provides an inexpensive way to expand microprocessors

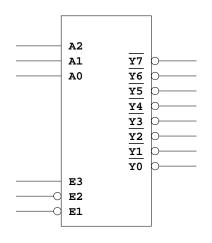

- One MSI device often used in such expansions is a decoder, such as the 74HC138 decoder chip

When E3 high, E2 and E1 low, one of the outputs of the 74138 will go low A2, A1, A0 determine which output will be low.

| A2 | <b>A1</b> | <b>A</b> 0 | Output |

|----|-----------|------------|--------|

| 0  | 0         | 0          | Y0     |

| 0  | 0         | 1          | Y1     |

| 0  | 1         | 0          | Y2     |

| 0  | 1         | 1          | ¥3     |

| 1  | 0         | 0          | ¥4     |

| 1  | 0         | 1          | ¥5     |

| 1  | 1         | 0          | Y6     |

| 1  | 1         | 1          | ¥7     |