Up: Lab 4: Adder/Subtractor

Previous: 2 Lab

Subsections

3 Supplementary Material

3.1 Verilog

In the previous lab you have defined a half adder by instantiating primitive

gates. As the design becomes more and more complex, it is convenient to create

separate modules and then combine them in one file. For example, in the

previous lab you have created a half adder module and in this lab you will

create a full adder/subtractor which can be designed by using the half adder

module. So, in this lab you will instantiate two half adders to form the full

adder, then instantiate four full adders to create the 4-bit adder/subtractor.

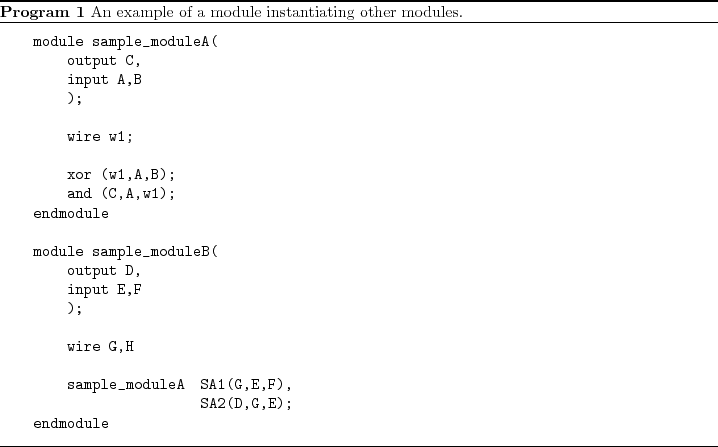

Program 1 illustrates this concept.

In this sample program the module sample_moduleA is instantiated twice as

SA1 and SA2 in the higher level module sample_moduleB.

Copyright © 2008, Electrical Engineering Department, New Mexico Tech

Last Modified 2009-09-23