Up: 3 Supplementary Material

Previous: 3.1 More on Verilog

Subsections

3.2 Verilog - Behavioral Modeling

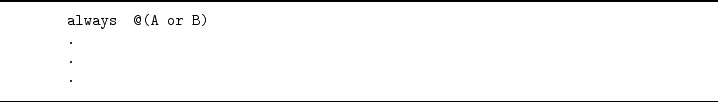

- Behavioral modeling use the keyword always.

- Target output is of type reg. Unlike a wire, reg is updated only when a new value is assigned. In other words,

it is not continuously updated as wire data types.

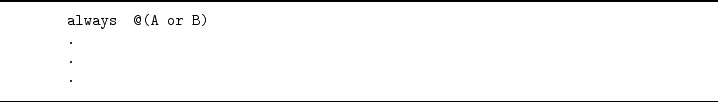

- always may be followed by an event control expression.

- always is followed by the symbol

followed by a list of

variables. Each time there is a change in those variables, the always block is executed.

followed by a list of

variables. Each time there is a change in those variables, the always block is executed.

- There is no semicolon at the end of the always block.

- The list of variables are separated by logical operator or and not bitwise OR operator ''|''.

- Below is an example of an always block.

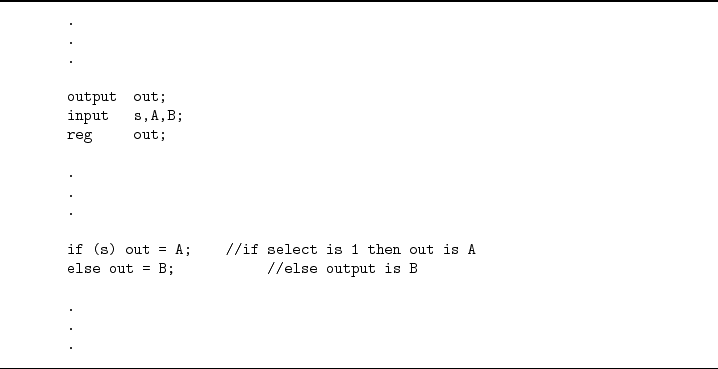

if-else statements provide means for a conditional output based on

the arguments of the if statement.

case Statements provide an easy way to represent a multi-branch

conditional statement.

- The first statement that makes a match is executed.

- Unspecified bit patterns could be treated using default

keyword.

Up: 3 Supplementary Material

Previous: 3.1 More on Verilog

Copyright © 2008, Electrical Engineering Department, New Mexico Tech

Last Modified 2009-09-22